# MEMORY Mobile FCRAM<sup>TM</sup> cmos

# 128 M Bit (8 M word×16 bit)

Mobile Phone Application Specific Memory

# MB82DBR08163A-70L

#### **■ DESCRIPTION**

The FUJITSU MB82DBR08163A is a CMOS Fast Cycle Random Access Memory (FCRAM\*) with asynchronous Static Random Access Memory (SRAM) interface containing 134,217,728 storages accessible in a 16-bit format. MB82DBR08163A is utilized using a FUJITSU advanced FCRAM core technology and improved integration in comparison to regular SRAM.

The MB82DBR08163A adopts asynchronous page mode and synchronous burst mode for fast memory access as user configurable options.

This MB82DBR08163A is suited for mobile applications such as Cellular Handset and PDA.

\*: FCRAM is a trademark of FUJITSU LIMITED, Japan

### **■ PRODUCT LINEUP**

| Parameter                        | MB82DBR08163A-70L |

|----------------------------------|-------------------|

| Access Time (Max) (tce, taa)     | 70 ns             |

| CLK Access Time (Max) (tac)      | 11 ns             |

| Active Current (Max) (IDDA1)     | 35 mA             |

| Standby Current (Max) (IDDS1)    | 300 μΑ            |

| Power Down Current (Max) (IDDPS) | 10 μΑ             |

#### **■ FEATURES**

- Asynchronous SRAM Interface

- Fast Access Time : tce = 70 ns Max

- 8 words Page Access Capability: tPAA = 20 ns Max

- Burst Read/Write Access Capability: t<sub>AC</sub> = 11 ns Max

- Low Voltage Operating Condition: VDD = 2.6 V to 3.1 V

$V_{DDQ} = 1.65 \text{ V to } 1.95 \text{ V}$

- Wide Operating Temperature : T<sub>A</sub> = -30 °C to +85 °C

- Byte Control by LB and UB

- Low-Power Consumption : IDDA1 = 35 mA Max

$I_{DDS1} = 300 \mu A Max$

• Various Power Down mode : Sleep

16 M-bit Partial

32 M-bit Partial

Shipping Form: Wafer/Chip

### **■ PIN DESCRIPTION**

| Pin Name                            | Description                      |

|-------------------------------------|----------------------------------|

| A <sub>22</sub> to A <sub>0</sub>   | Address Input                    |

| CE1                                 | Chip Enable 1 (Low Active)       |

| CE2                                 | Chip Enable 2(High Active)       |

| WE                                  | Write Enable (Low Active)        |

| ŌĒ                                  | Output Enable (Low Active)       |

| LB                                  | Lower Byte Control (Low Active)  |

| ŪB                                  | Upper Byte Control (Low Active)  |

| CLK                                 | Clock Input                      |

| ĀDV                                 | Address Valid Input (Low Active) |

| WAIT                                | Wait Output                      |

| DQ <sub>8</sub> to DQ <sub>1</sub>  | Lower Byte Data Input/Output     |

| DQ <sub>16</sub> to DQ <sub>9</sub> | Upper Byte Data Input/Output     |

| V <sub>DD</sub>                     | Power Supply Voltage             |

| Vddq                                | I/O Power Supply Voltage         |

| Vss                                 | Ground                           |

Note: Refer to "■PACKAGE FOR ENGINEERING SAMPLES" for additional pin descriptions of FBGA package supply.

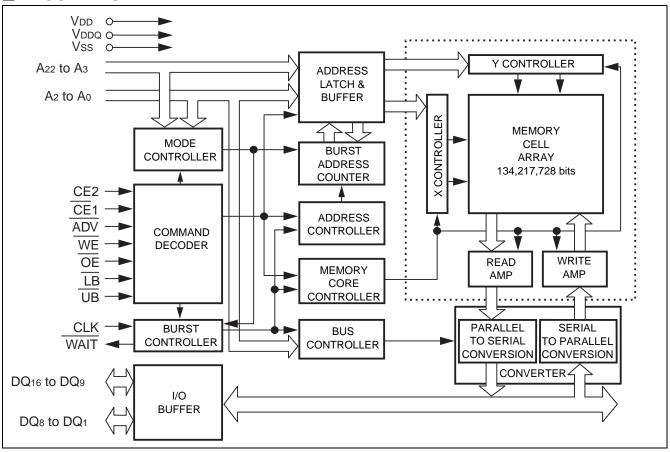

### **■ BLOCK DIAGRAM**

#### **■ FUNCTION TRUTH TABLE**

### 1. Asynchronous Operation (Page Mode)

| Mode                        | CE2 | CE <sub>1</sub> | CLK | ADV | WE | OE  | LB  | UB  | A <sub>22</sub> to A <sub>0</sub> | DQ <sub>8</sub> to DQ <sub>1</sub> | DQ <sub>16</sub> to DQ <sub>9</sub> | WAIT   |

|-----------------------------|-----|-----------------|-----|-----|----|-----|-----|-----|-----------------------------------|------------------------------------|-------------------------------------|--------|

| Standby<br>(Deselect)       | Н   | Н               | Х   | Х   | Х  | Х   | Х   | Х   | Х                                 | High-Z                             | High-Z                              | High-Z |

| Output Disable*1            |     |                 | Х   | *3  | Н  | Н   | Х   | Х   | *5                                | High-Z                             | High-Z                              | High-Z |

| Output Disable<br>(No Read) |     |                 | Х   | *3  |    |     | Н   | Н   | Valid                             | High-Z                             | High-Z                              | High-Z |

| Read (Upper Byte)           |     |                 | Х   | *3  |    |     | Н   | L   | Valid                             | High-Z                             | Output<br>Valid                     | High-Z |

| Read (Lower Byte)           |     |                 | Х   | *3  | Н  | L   | L   | Н   | Valid                             | Output<br>Valid                    | High-Z                              | High-Z |

| Read (Word)                 | Н   | L               | Х   | *3  |    |     | L   | L   | Valid                             | Output<br>Valid                    | Output<br>Valid                     | High-Z |

| Page Read                   |     |                 | Х   | *3  |    |     | L/H | L/H | Valid                             | *6                                 | *6                                  | High-Z |

| No Write                    |     |                 | Х   | *3  |    |     | Н   | Н   | Valid                             | Invalid                            | Invalid                             | High-Z |

| Write (Upper Byte)          |     |                 | Χ   | *3  |    |     | Н   | L   | Valid                             | Invalid                            | Input Valid                         | High-Z |

| Write (Lower Byte)          |     |                 | Х   | *3  | L  | H*4 | L   | Н   | Valid                             | Input<br>Valid                     | Invalid                             | High-Z |

| Write (Word)                |     |                 | Х   | *3  | •  |     | L   | L   | Valid                             | Input<br>Valid                     | Input Valid                         | High-Z |

| Power Down*2                | L   | Х               | Х   | Х   | Х  | Х   | Х   | Х   | Х                                 | High-Z                             | High-Z                              | High-Z |

Note :  $L = V_{IL}$ ,  $H = V_{IH}$ , X can be either  $V_{IL}$  or  $V_{IH}$ , High-Z = High Impedance

- \*2: Power Down mode can be entered from Standby state and all output are in High-Z state. Data retention depends on the selection of Partial Size for Power Down Program. Refer to "Power Down" in "■FUNCTIONAL DESCRIPTION" for the details.

- \*3: "L" for address pass through and "H" for address latch on the rising edge of ADV.

- \*4 : OE can be V<sub>L</sub> during write operation if the following conditions are satisfied;

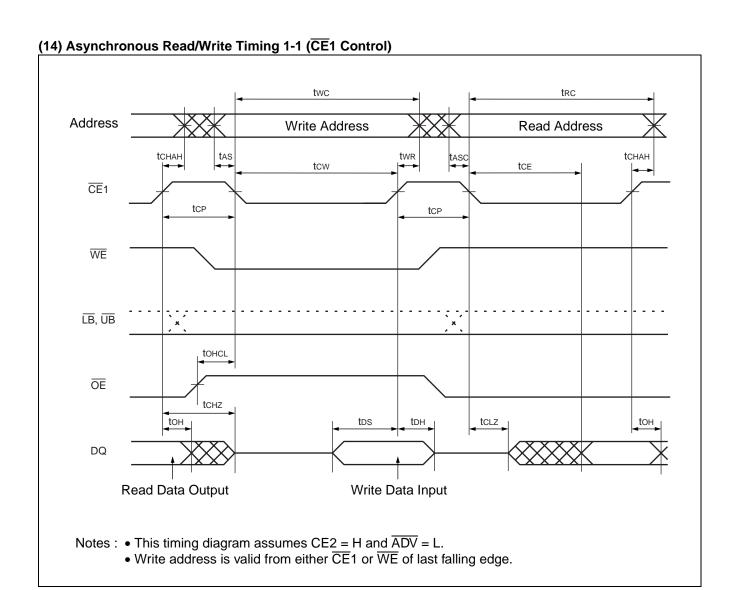

- (1) Write pulse is initiated by CE1. See "(14) Asynchronous Read/Write Timing 1-1 (CE1 Control)" in "■TIMING DIAGRAMS".

- (2) OE stays V<sub>IL</sub> during Write cycle.

- \*5 : Can be either V<sub>IL</sub> or V<sub>IH</sub> but must be valid before Read or Write.

- \*6: Output of upper and lower byte data is either Valid or High-Z depending on the level of  $\overline{LB}$  and  $\overline{UB}$  input.

<sup>\*1:</sup> Should not be kept this logic condition longer than 1 µs.

2. Synchronous Operation (Burst Mode)

| Mode                                     | CE2 | CE1 | CLK | ADV      | WE  | OE  | LB   | UB   | A22 to A0 | DQ8 to DQ1        | DQ <sub>16</sub> to DQ <sub>9</sub> | WAIT                |

|------------------------------------------|-----|-----|-----|----------|-----|-----|------|------|-----------|-------------------|-------------------------------------|---------------------|

| Standby(Deselect)                        |     | Н   | Х   | Х        | Χ   | Χ   | Χ    | Χ    | Χ         | High-Z            | High-Z                              | High-Z              |

| Start Address Latch*1                    |     |     |     | <b>™</b> | X*4 | X*4 |      |      | Valid*7   | High-Z*8          | High-Z*8                            | High-Z*11           |

| Advance Burst Read to<br>Next Address*1  |     |     | *3  |          |     | L   |      |      |           | Output<br>Valid*9 | Output<br>Valid*9                   | Output<br>Valid     |

| Burst Read<br>Suspend*1                  | Н   | L   | *3  |          | Н   | Н   | V/+6 | V/+6 |           | High-Z            | High-Z                              | High*12             |

| Advance Burst Write to<br>Next Address*1 |     |     | *3  | Н        | L*5 | Н   | X*6  | X*6  | Х         | Input<br>Valid*10 | Input<br>Valid*10                   | High* <sup>13</sup> |

| Burst Write Suspend*1                    |     |     | *3  |          | H*5 | П   |      |      |           | Input<br>Invalid  | Input<br>Invalid                    | High*12             |

| Terminate Burst Read                     |     | 丕   | Х   |          | Н   | Χ   |      |      |           | High-Z            | High-Z                              | High-Z              |

| Terminate Burst Write                    |     | 丕   | Х   |          | Х   | Н   |      |      |           | High-Z            | High-Z                              | High-Z              |

| Power Down*2                             | L   | Х   | Х   | Х        | Х   | Χ   | Χ    | Χ    | Х         | High-Z            | High-Z                              | High-Z              |

Note : L =  $V_{IL}$ , H =  $V_{IH}$ , X can be either  $V_{IL}$  or  $V_{IH}$ ,  $\sqrt{\phantom{}}$  = valid edge,  $\sqrt{\phantom{}}$  = rising edge of Low pulse, High-Z = High impedance

- $^{*1}$ : Should not be kept this logic condition longer than 4  $\mu s$ .

- \*2 : Power Down mode can be entered from Standby state and all output are in High-Z state.

Data retention depends on the selection of Partial Size for Power Down Program.

Refer to "Power Down" in "■FUNCTIONAL DESCRIPTION" for the details.

- \*3 : Valid clock edge shall be set on either rising or falling edge through CR set. CLK must be started and stable prior to memory access.

- \*4 : Can be either  $V_{IL}$  or  $V_{IH}$  except for the case the both of  $\overline{OE}$  and  $\overline{WE}$  are  $V_{IL}$ . It is prohibited to bring the both of  $\overline{OE}$  and  $\overline{WE}$  to  $V_{IL}$ .

- \*5 : When device is operating in "WE Single Clock Pulse Control" mode, WE is don't care once write operation is determined by WE Low Pulse at the beginning of write access together with address latching. Burst write suspend feature is not supported in "WE Single Clock Pulse Control" mode.

- \*6 : Can be either V<sub>IL</sub> or V<sub>IH</sub> but must be valid before Read or Write is determined. And once LB and UB input levels are determined, they must not be changed until the end of burst.

- \*7 : Once valid address is determined, input address must not be changed during  $\overline{ADV} = L$ .

- \*8 : If  $\overline{OE} = L$ , output is either Invalid or High-Z depending on the level of  $\overline{LB}$  and  $\overline{UB}$  input. If  $\overline{WE} = L$ , input is Invalid. If  $\overline{OE} = \overline{WE} = H$ , output is High-Z.

- \*9 : Outputs is either Valid or High-Z depending on the level of  $\overline{LB}$  and  $\overline{UB}$  input.

- \*10: Input is either Valid or Invalid depending on the level of LB and UB input.

- \*11 : Output is either High-Z or Invalid depending on the level of  $\overline{\text{OE}}$  and  $\overline{\text{WE}}$  input.

- \*12 : Keep the level from previous cycle except for suspending on last data. Refer to "WAIT Output Function" in "■FUNCTIONAL DESCRIPTION" for the details.

- \*13: WAIT output is driven in High level during burst write operation.

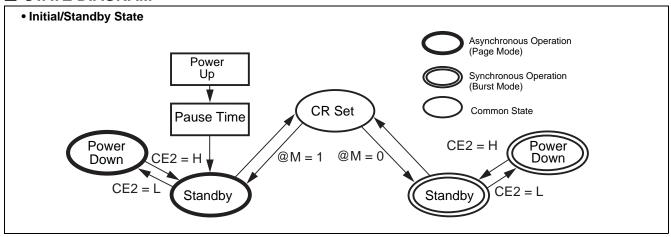

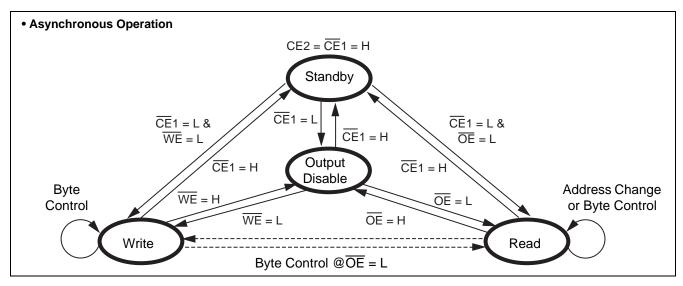

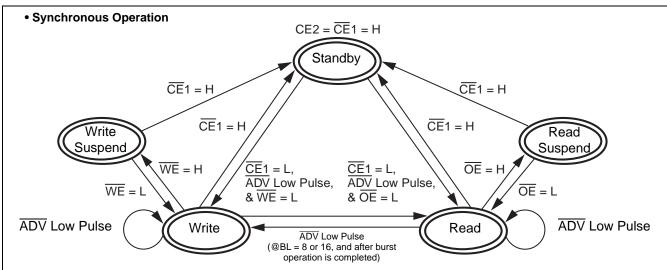

#### **■ STATE DIAGRAM**

Note: Assuming all the parameters specified in AC CHARACTERISTICS are satisfied. Refer to the "■FUNCTIONAL DESCRIPTION", "2. AC Characteristics" in "■ELECTRICAL CHARACTERISTICS", and "■TIMING DIAGRAMS" for details.

#### **■ FUNCTIONAL DESCRIPTION**

This device supports asynchronous read, page read & normal write operation and synchronous burst read and burst write operation for faster memory access and features three kinds of power down modes for power saving as user configurable option.

#### • Power-up

It is required to follow the power-up timing to start executing proper device operation. Refer to "Power-up Timing". After Power-up, the device defaults to asynchronous page read & normal write operation mode with sleep power down feature.

#### • Configuration Register

The Configuration Register(CR) is used to configure the type of device function among optional features. Each selection of features is set through CR set sequence after power-up. If CR set sequence is not performed after power-up, the device is configured for asynchronous operation with sleep power down feature as default configuration.

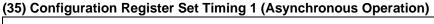

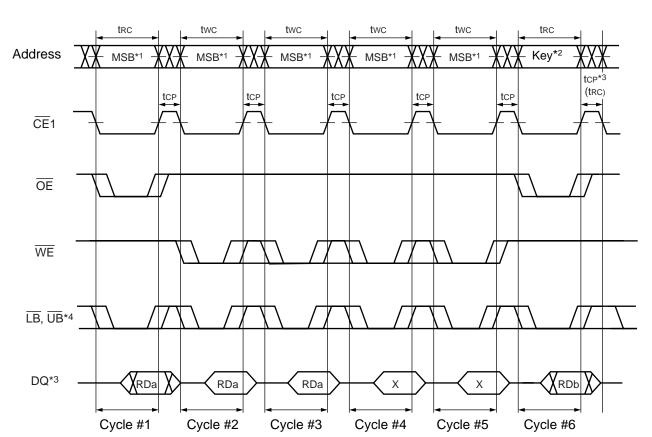

#### CR Set Sequence

The CR set requires total 6 read/write cycles with unique address. Operation other than read/write operation requires that device being in standby mode. Following table shows the detail sequence.

| Cycle # | Operation | Address      | Data            |

|---------|-----------|--------------|-----------------|

| #1      | Read      | 7FFFFh (MSB) | Read Data (RDa) |

| #2      | Write     | 7FFFFh       | RDa             |

| #3      | Write     | 7FFFFh       | RDa             |

| #4      | Write     | 7FFFFh       | Х               |

| #5      | Write     | 7FFFFh       | X               |

| #6      | Read      | Address Key  | Read Data (RDb) |

The first cycle is to read from most significant address(MSB).

The second and third cycles are to write to MSB. If the second or third cycle is written into the different address, the CR set is cancelled and the data written by the second or third cycle is valid as a normal write operation. It is recommended to write back the data(RDa) read by first cycle to MSB in order to secure the data.

The forth and fifth cycles are to write to MSB. The data of forth and fifth cycles is don't-care. If the forth or fifth cycle is written into different address, the CR set is also cancelled, but write data may not be written as normal write operation.

The last cycle is to read from specific address key for mode selection. And read data(RDb) is invalid.

Once this CR set sequence is performed from an initial CR set to the other new CR set, the written data stored in memory cell array may be lost. So, it should perform the CR set sequence prior to regular read/write operation if necessary to change from default configuration.

### • Address Key

The address key has the following format.

| Address<br>Pin                     | Register<br>Name                   | Function        | Key | Description                                                  | Note |

|------------------------------------|------------------------------------|-----------------|-----|--------------------------------------------------------------|------|

| A <sub>22</sub> , A <sub>21</sub>  | _                                  | _               | 1   | Unused bits must be 1                                        | *1   |

|                                    |                                    |                 | 00  | 32 M-bit Partial                                             |      |

| ۸., ۸.,                            | to A <sub>16</sub> PS Partial Size |                 | 01  | 16 M-bit Partial                                             |      |

| A20, A19                           | F3                                 | Partial Size    | 10  | Reserved for future use                                      | *2   |

|                                    |                                    |                 | 11  | Sleep [Default]                                              |      |

|                                    |                                    |                 | 000 | Reserved for future use                                      | *2   |

|                                    |                                    |                 | 001 | Reserved for future use                                      | *2   |

|                                    |                                    |                 | 010 | 8 words                                                      |      |

| A <sub>18</sub> to A <sub>16</sub> | RI                                 | Ruret Length    | 011 | 16 words                                                     |      |

| A18 10 A16                         | DL                                 | Buist Length    | 100 | Reserved for future use                                      | *2   |

|                                    |                                    |                 | 101 | Reserved for future use                                      | *2   |

|                                    |                                    | Л Mode          |     | Reserved for future use                                      | *2   |

|                                    |                                    |                 | 111 | Continuous                                                   |      |

| A <sub>15</sub>                    | М                                  | Mode            | 0   | Synchronous Mode (Burst Read / Write)                        | *3   |

| Als                                | 101                                | Wiode           | 1   | Asynchronous Mode [Default] (Page Read / Normal Write)       | *4   |

|                                    |                                    |                 | 000 | Reserved for future use                                      | *2   |

|                                    |                                    |                 | 001 | 3 clocks                                                     |      |

| A <sub>14</sub> to A <sub>12</sub> | RL                                 | Read Latency    | 010 | 4 clocks                                                     |      |

|                                    |                                    |                 | 011 | 5 clocks                                                     |      |

|                                    |                                    |                 | 1xx | Reserved for future use                                      | *2   |

| <b>A</b> 11                        | BS                                 | Burst Sequence  | 0   | Reserved for future use                                      | *2   |

| 7 (11                              | ВО                                 | Barst Ocquerioc | 1   | Sequential                                                   |      |

| <b>A</b> 10                        | SW                                 | Single Write    | 0   | Burst Read & Burst Write                                     |      |

| 7110                               | 011                                | Cirigio Willo   | 1   | Burst Read & Single Write                                    | *5   |

| <b>A</b> 9                         | VE                                 | Valid Clock     | 0   | Falling Clock Edge                                           |      |

| 710                                | , L                                | Edge            | 1   | Rising Clock Edge                                            |      |

| <b>A</b> 8                         |                                    | _               | 1   | Unused bits must be 1                                        | *1   |

| <b>A</b> 7                         | WC                                 | Write Control   | 0   | WE Single Clock Pulse Control without Write Suspend Function | *5   |

|                                    |                                    |                 | 1   | WE Level Control with Write Suspend Function                 |      |

| A <sub>6</sub> to A <sub>0</sub>   |                                    | _               | 1   | Unused bits must be 1                                        | *1   |

<sup>\*1:</sup>  $A_{22}$ ,  $A_{21}$ ,  $A_{8}$  and  $A_{6}$  to  $A_{0}$  must be all "1" in any cases.

<sup>\*2:</sup> It is prohibited to apply this key.

<sup>\*3:</sup> If M = 0, all the registers must be set with appropriate Key input at the same time.

<sup>\*4:</sup> If M = 1, PS must be set with appropriate Key input at the same time. Except for PS, all the other key inputs must be "1".

<sup>\*5:</sup> Burst Read & Single Write is not supported at WE Single Clock Pulse Control.

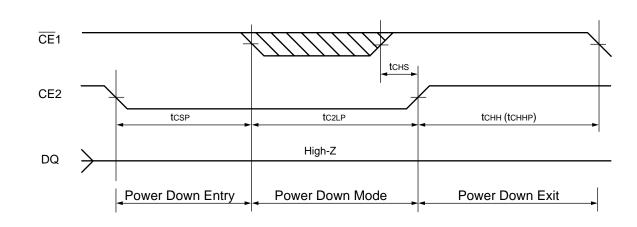

#### • Power Down

The Power Down is low power idle state controlled by CE2. CE2 Low drives the device in power down mode and maintains low power idle state as long as CE2 is kept Low. CE2 High resumes the device from power down mode.

This device has three power down modes, Sleep, 16 M-bit Partial, and 32 M-bit Partial.

The selection of power down mode is set through CR set sequence. Each mode has following data retention features.

| Mode             | Data Retention Size | Retention Address  |

|------------------|---------------------|--------------------|

| Sleep [default]  | No                  | N/A                |

| 16 M-bit Partial | 16 M bits           | 000000h to 0FFFFh  |

| 32 M-bit Partial | 32 M bits           | 000000h to 1FFFFFh |

The default state after power-up is Sleep and it is the lowest power consumption but all data will be lost once CE2 is brought to Low for Power Down. It is not required to perform CR set sequence to set to Sleep mode after power-up in case of asynchronous operation.

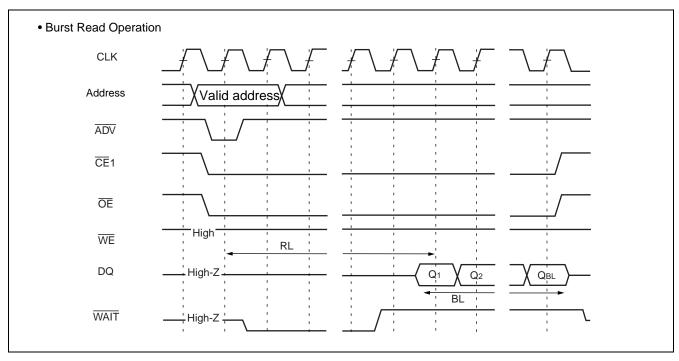

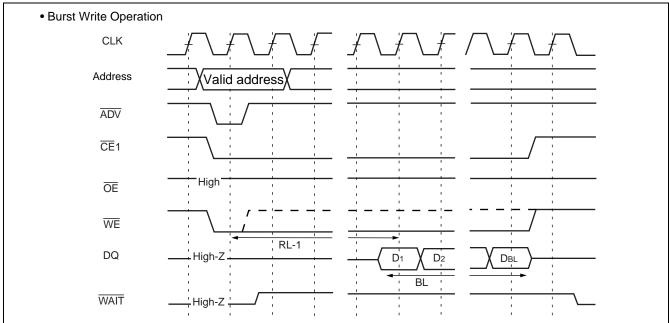

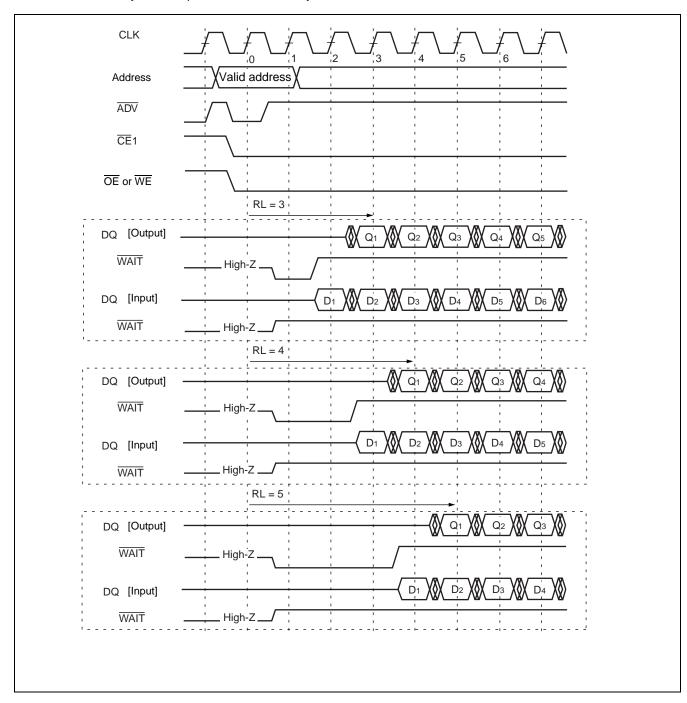

#### Burst Read/Write Operation

Synchronous burst read/write operation provides faster memory access that synchronized to microcontroller or system bus frequency. Configuration Register(CR) Set is required to perform burst read & write operation after power-up. Once CR set sequence is performed to select synchronous burst mode, the device is configured to synchronous burst read/write operation mode with corresponding RL and BL that is set through CR set sequence together with operation mode. In order to perform synchronous burst read & write operation, it is required to control new signals, CLK,  $\overline{\text{ADV}}$  and  $\overline{\text{WAIT}}$  that Low Power SRAMs don't have.

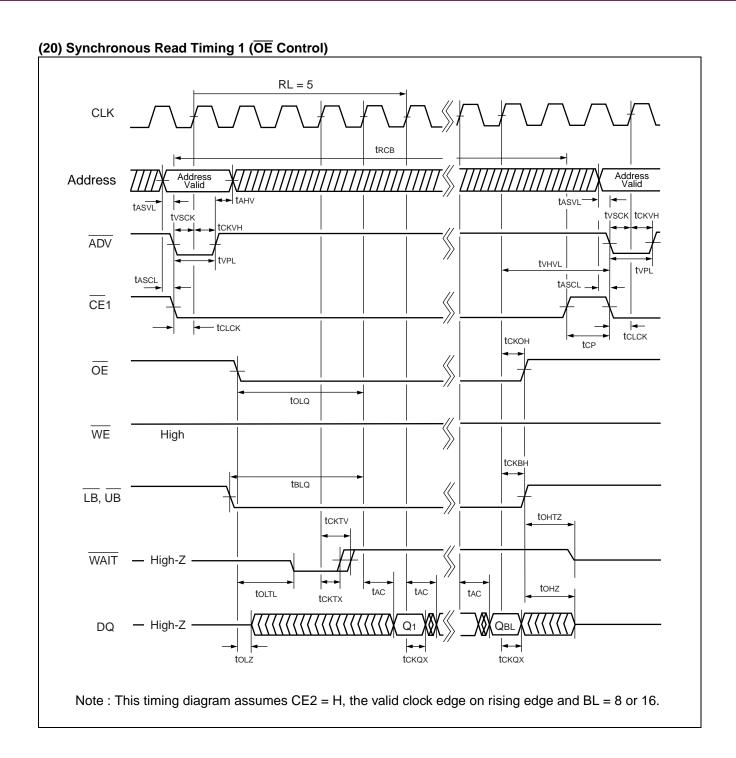

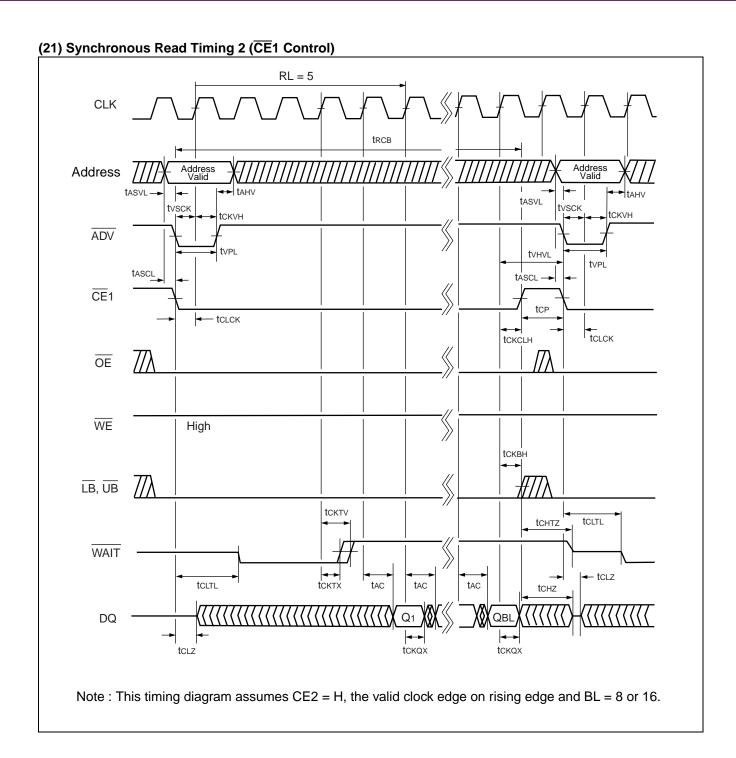

### • CLK Input Function

The CLK is input signal to synchronize memory to microcontroller or system bus frequency during synchronous burst read & write operation. The CLK input increments device internal address counter and the valid edge of CLK is referred for latency counts from address latch, burst write data latch, and burst read data output. During synchronous operation mode, CLK input must be supplied except for standby state and power down state. CLK is don't care during asynchronous operation.

#### • ADV Input Function

The  $\overline{ADV}$  is input signal to latch valid address. It is applicable to synchronous operation as well as asynchronous operation.  $\overline{ADV}$  input is active during  $\overline{CE1} = L$  and  $\overline{CE1} = H$  disables  $\overline{ADV}$  input. All addresses are determined on the rising edge of  $\overline{ADV}$ .

During synchronous burst read/write operation,  $\overline{ADV} = H$  disables all address inputs. Once  $\overline{ADV}$  is brought to High after valid address latch, it is inhibited to bring  $\overline{ADV}$  Low until the end of burst or until burst operation is terminated.  $\overline{ADV}$  Low pulse is mandatory for synchronous burst read/write operation mode to latch the valid address input.

During asynchronous operation,  $\overline{ADV} = H$  also disables all address inputs.  $\overline{ADV}$  can be tied to Low during asynchronous operation and it is not necessary to control  $\overline{ADV}$  to High.

### • WAIT Output Function

The WAIT is output signal to indicate data bus status when the device is operating in synchronous burst mode.

During burst read operation,  $\overline{WAIT}$  output is enabled after specified time duration from  $\overline{OE} = L$  or  $\overline{CE1} = L$  whichever occurs last.  $\overline{WAIT}$  output Low indicates data output at next clock cycle is invalid, and  $\overline{WAIT}$  output becomes High one clock cycle prior to valid data output. During  $\overline{OE}$  read suspend,  $\overline{WAIT}$  output doesn't indicate data bus status but carries the same level from previous clock cycle (kept High) except for burst read suspend on the final data output. If final read data output is suspended,  $\overline{WAIT}$  output becomes high impedance after specified time duration from  $\overline{OE} = H$ .

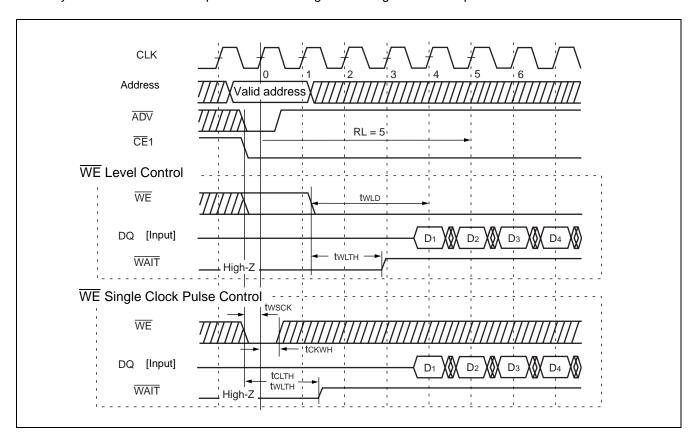

During burst write operation,  $\overline{WAIT}$  output is valid to High level after specified time duration from  $\overline{WE}$  = L or  $\overline{CE1}$  = L whichever occurs last and kept High for entire write cycles including  $\overline{WE}$  write suspend. The actual write data latching starts on the appropriate clock edge with respect to Valid Clock Edge, Read Latency, and Burst Length. During  $\overline{WE}$  write suspend,  $\overline{WAIT}$  output doesn't indicate data bus status but carries the same level from previous clock cycle (kept High) except for write suspend on the final data input. If final write data input is suspended,  $\overline{WAIT}$  output becomes high impedance after specified time duration from  $\overline{WE}$  = H.

This device doesn't incur additional output delay against crossing device-row boundary or internal refresh operation. Therefore, the burst operation is always started after fixed latency with respect to read latency. And there is no waiting cycle asserted in the middle of burst operation except for burst read or write suspend by  $\overline{\text{OE}}$  brought to High or  $\overline{\text{WE}}$  brought to High. Thus, once  $\overline{\text{WAIT}}$  output is enabled and brought to High,  $\overline{\text{WAIT}}$  output keeps High level until the end of burst or until the burst operation is terminated.

When the device is operating in asynchronous mode, WAIT output is always in High Impedance.

#### Latency

Read Latency (RL) is the number of clock cycles between the address being latched and first read data becoming available during synchronous burst read operation. It is set through CR set sequence after power-up. Once specific RL is set through CR set sequence, write latency, that is the number of clock cycles between address being latched and first write data being latched, is automatically set to RL-1. The burst operation is always started after fixed latency with respect to Read Latency set in CR.

### Address Latch by ADV

The  $\overline{ADV}$  latches valid address presence on address inputs. During synchronous burst read/write operation mode, all the address are determined on the rising edge of  $\overline{ADV}$  when  $\overline{CE}1 = L$ . The specified minimum value of  $\overline{ADV} = L$  setup time and hold time against valid edge of clock where RL count is begun must be satisfied. Valid address must be determined with specified setup time against either the falling edge of  $\overline{ADV}$  or falling edge of  $\overline{CE}1$  whichever comes late. And the determined valid address must not be changed during  $\overline{ADV} = L$  period.

#### • Burst Length

Burst Length is the number of word to be read or written during synchronous burst read/write operation as the result of a single address latch cycle. It can be set on 8,16 words boundary or continuous for entire address through CR set sequence. The burst type is sequential that is incremental decoding scheme within a boundary address. Starting from initial address being latched, device internal address counter assigns +1 to the previous address until reaching the end of boundary address and then wrap round to least significant address (= 0). After completing read data output or write data latch for the set burst length, operation automatically ended except for continuous burst length. When continuous burst length is set, read/write is endless unless it is terminated by the rising edge of  $\overline{\text{CE}}1$ .

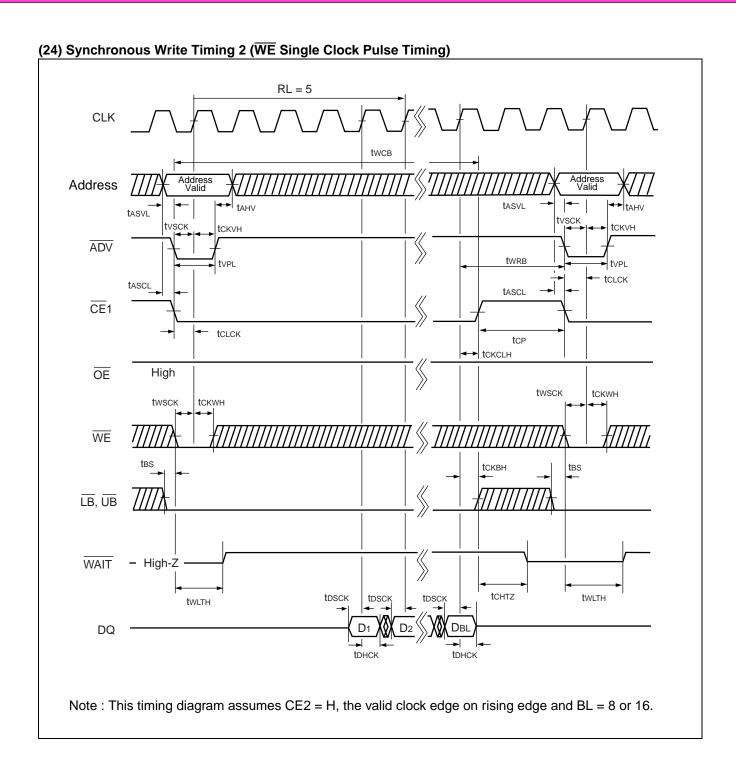

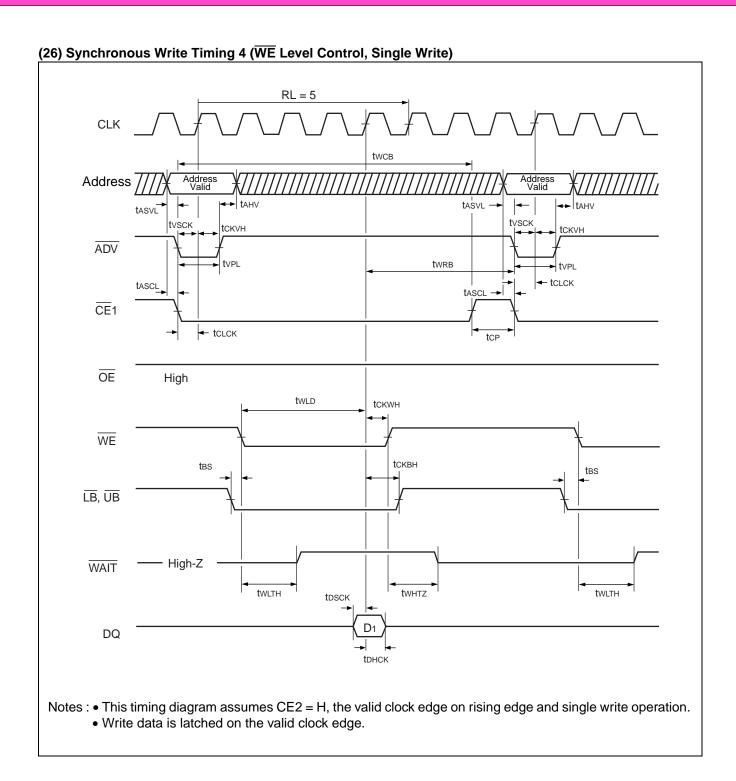

#### • Single Write

Single write is synchronous write operation with Burst Length = 1. The device can be configured either to "Burst Read & Single Write" or to "Burst Read & Burst Write" through CR set sequence. Once the device is configured to "Burst Read & Single Write" mode, the burst length for synchronous write operation is always fixed 1 regardless of BL values set in CR, while burst length for read is in accordance with BL values set in CR.

#### • Write control

The device has two types of WE signal control method, "WE Level Control" and "WE Single Clock Pulse Control", for synchronous burst write operation. It is configured through CR set sequence.

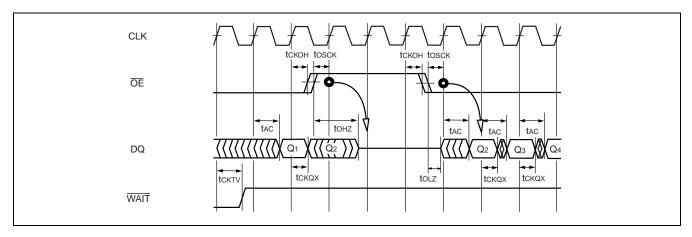

#### Burst Read Suspend

Burst read operation can be suspended by  $\overline{OE}$  High pulse. During burst read operation,  $\overline{OE}$  brought to High from Low suspends burst read operation. Once  $\overline{OE}$  is brought to High with the specified setup time against clock where the data being suspended, the device internal counter is suspended, and the data output becomes high impedance after specified time duration. It is inhibited to suspend the first data output at the beginning of burst read.

$\overline{\text{OE}}$  brought to Low from High resumes burst read operation. Once  $\overline{\text{OE}}$  is brought to Low, data output becomes valid after specified time duration, and internal address counter is reactivated. The last data output being suspended as the result of  $\overline{\text{OE}}$  = H and first data output as the result of  $\overline{\text{OE}}$  = L are from the same address.

In order to guarantee to output last data before suspension and first data after resumption, the specified minimum value of  $\overline{OE}$  hold time and  $\overline{OE}$  setup time against clock edge must be satisfied respectively.

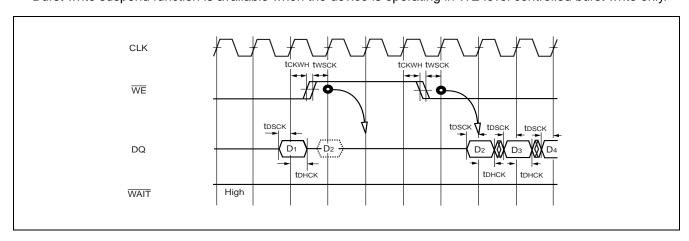

#### • Burst Write Suspend

Burst write operation can be suspended by  $\overline{\text{WE}}$  High pulse. During burst write operation,  $\overline{\text{WE}}$  brought to High from Low suspends burst write operation. Once  $\overline{\text{WE}}$  is brought to High with the specified setup time against clock where the data being suspended, device internal counter is suspended, data input is ignored. It is inhibited to suspend the first data input at the beginning of burst write.

$\overline{\text{WE}}$  brought to Low from High resumes burst write operation. Once  $\overline{\text{WE}}$  is brought to Low, data input becomes valid after specified time duration, and internal address counter is reactivated. The write address of the cycle where data being suspended and the first write address as the result of  $\overline{\text{WE}} = \text{L}$  are the same address.

In order to guarantee to latch the last data input before suspension and first data input after resumption, the specified minimum value of  $\overline{\text{WE}}$  hold time and  $\overline{\text{WE}}$  setup time against clock edge must be satisfied respectively. Burst write suspend function is available when the device is operating in  $\overline{\text{WE}}$  level controlled burst write only.

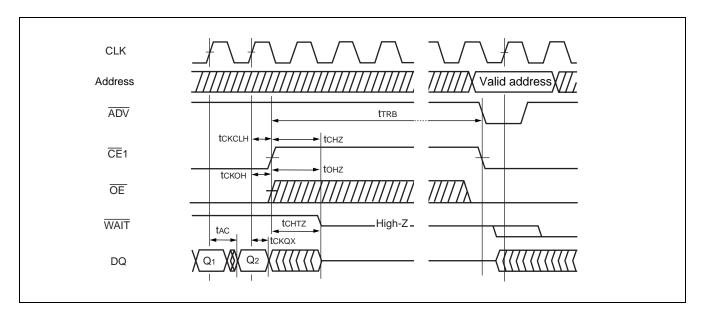

#### Burst Read Termination

Burst read operation can be terminated by  $\overline{CE}1$  brought to High. If BL is set on Continuous, burst read operation is continued endless unless terminated by  $\overline{CE}1$  = H. It is inhibited to terminate burst read before first data output is completed. In order to guarantee last data output, the specified minimum value of  $\overline{CE}1$  = L hold time from clock edge must be satisfied. After termination, the specified minimum recovery time ( $t_{TRB}$ ) is required to start new access.

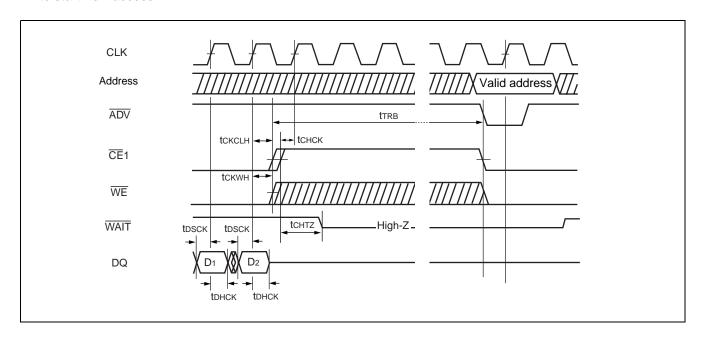

#### Burst Write Termination

Burst write operation can be terminated by  $\overline{CE}1$  brought to High. If BL is set on Continuous, burst write operation is continued endless unless terminated by  $\overline{CE}1$  = H. It is inhibited to terminate burst write before first data input is completed. In order to guarantee last data input being latched, the specified minimum values of  $\overline{CE}1$  = L hold time from clock edge must be satisfied. After termination, the specified minimum recovery time ( $t_{TRB}$ ) is required to start new access.

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                                | Symbol           | Rat         | ing   | Unit |

|------------------------------------------|------------------|-------------|-------|------|

| Farameter                                | Symbol           | Min         | Max   | Unit |

| Voltage of VDD Supply Relative to Vss *  | V <sub>DD</sub>  | - 0.5       | + 3.6 | V    |

| Voltage of VDDQ Supply Relative to Vss * | V <sub>DDQ</sub> | - 0.5       | + 2.6 | V    |

| Voltage at Any Pin Relative to Vss *     | VIN, VOUT        | - 0.5       | + 2.6 | V    |

| Short Circuit Output Current             | Іоит             | - 50        | + 50  | mA   |

| Storage Temperature                      | Tstg             | <b>- 55</b> | + 125 | °C   |

<sup>\* :</sup> All voltages are referenced to Vss = 0 V.

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### **■ RECOMMENDED OPERATING CONDITIONS**

| Parameter                      | Symbol           | Va                   | lue                    | l lnit |

|--------------------------------|------------------|----------------------|------------------------|--------|

|                                | Symbol           | Min                  | Max                    | Unit   |

| Power Supply Voltage*1         | V <sub>DD</sub>  | 2.6                  | 3.1                    | V      |

| I/O Power Supply Voltage*1     | V <sub>DDQ</sub> | 1.65                 | 1.95                   | V      |

| Ground                         | Vss              | 0                    | 0                      | V      |

| High Level Input Voltage*1, *2 | VIH              | $V_{DDQ} \times 0.8$ | V <sub>DDQ</sub> + 0.2 | V      |

| Low Level Input Voltage*1, *3  | VıL              | - 0.3                | V <sub>DDQ</sub> × 0.2 | V      |

| Ambient Temperature            | TA               | - 30                 | + 85                   | °C     |

<sup>\*1 :</sup> All voltages are referenced to Vss = 0 V.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

<sup>\*2 :</sup> Maximum DC voltage on input and I/O pins is  $V_{DDQ}$  + 1.0 V. During voltage transitions, inputs may overshoot to  $V_{DDQ}$  + 1.0 V for periods of up to 5.0 ns.

<sup>\*3 :</sup> Minimum DC voltage on input or I/O pins is -0.3 V. During voltage transitions, inputs may undershoot Vss to -1.0 V for periods of up to 5.0 ns.

### **■ ELECTRICAL CHARACTERISTICS**

### 1. DC Characteristics

(At recommended operating conditions unless otherwise noted)

| Dorometer                       | Cumbal            | Symbol Test Conditions                                                                                                                                                                                                                                                |                                                                                                                                           |      | lue  | Unit |

|---------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| Parameter                       | Symbol            | lest Condition                                                                                                                                                                                                                                                        | Min                                                                                                                                       | Max  | Unit |      |

| Input Leakage Current           | lu                | $V_{SS} \leq V_{IN} \leq V_{DDQ}$                                                                                                                                                                                                                                     | -1.0                                                                                                                                      | +1.0 | μΑ   |      |

| Output Leakage Current          | Іго               | 0 V ≤ V <sub>OUT</sub> ≤ V <sub>DDQ</sub> ,<br>Output High Impedance                                                                                                                                                                                                  |                                                                                                                                           | -1.0 | +1.0 | μΑ   |

| Output High Voltage Level       | Vон               | $V_{DDQ} = V_{DDQ}$ (Min), $I_{OH} = -0.5$ (                                                                                                                                                                                                                          | mA                                                                                                                                        | 1.4  |      | V    |

| Output Low Voltage Level        | Vol               | lo <sub>L</sub> = 1 mA                                                                                                                                                                                                                                                |                                                                                                                                           | _    | 0.4  | V    |

|                                 | IDDPS             | V <sub>DD</sub> = V <sub>DD</sub> (Max), SLEEP                                                                                                                                                                                                                        |                                                                                                                                           |      | 10   | μΑ   |

| VDD Power Down Current          | IDDP16            | Vddq = Vddq (Max),<br>  Vin = Vih or Vil,                                                                                                                                                                                                                             | 16 M-bit Partial                                                                                                                          |      | 120  | μΑ   |

|                                 | IDDP32            | CE2 ≤ 0.2 V                                                                                                                                                                                                                                                           | 32 M-bit Partial                                                                                                                          | _    | 150  | μΑ   |

|                                 | IDDS              |                                                                                                                                                                                                                                                                       | /DD = VDD (Max), VDDQ = VDDQ (Max),<br>/IN (including CLK) = VIH or VIL,                                                                  |      | 1.5  | mA   |

| V <sub>DD</sub> Standby Current | IDDS1             | $\begin{split} & V_{\text{DD}} = V_{\text{DD}}  (\text{Max}),  V_{\text{DDQ}} = V_{\text{DDQ}} \\ & V_{\text{IN}}  (\text{including CLK}) \leq 0.2   \text{V or} \\ & \frac{V_{\text{IN}}}{\text{CE}1} = \text{CE2} \geq V_{\text{DDQ}} - 0.2   \text{V} \end{split}$ | _                                                                                                                                         | 300  | μА   |      |

|                                 | IDDS2             |                                                                                                                                                                                                                                                                       | $V_{DD} = V_{DD}$ (Max), $V_{DDQ} = V_{DDQ}$ (Max), $t_{CK} = Min$<br>$V_{IN} \le 0.2 \text{ V or } V_{IN} \ge V_{DDQ} - 0.2 \text{ V}$ , |      |      |      |

| V <sub>DD</sub> Active Current  | IDDA1             | VDD = VDD (Max),<br>VDDQ = VDDQ (Max),<br>VIN = VIH OR VIL,                                                                                                                                                                                                           | trc/twc = Min                                                                                                                             |      | 35   | mA   |

| VBB Active Guiterit             | I <sub>DDA2</sub> | $\overline{\text{CE}}$ 1 = V <sub>IL</sub> and CE2 = V <sub>IH</sub> ,<br>$\overline{\text{Iout}}$ = 0 mA                                                                                                                                                             | trc/twc = 1 μs                                                                                                                            | _    | 5    | mA   |

| VDD Page Read Current           | IDDA3             | $V_{DD} = V_{DD} \text{ (Max)}, V_{DDQ} = V_{DDQ} \text{ (Max)},$ $V_{IN} = V_{IH} \text{ or } V_{IL},$ $\overline{CE1} = V_{IL} \text{ and } CE2 = V_{IH},$ $I_{OUT} = 0 \text{ mA}, t_{PRC} = Min$                                                                  |                                                                                                                                           | _    | 15   | mA   |

| VDD Burst Access Current        | IDDA4             | $\begin{aligned} & V_{DD} = V_{DD} \text{ (Max), } V_{DDQ} = V_{DDQ} \\ & V_{IN} = V_{IH} \text{ or } V_{IL}, \\ & \overline{CE}1 = V_{IL} \text{ and } CE2 = V_{IH}, \\ & t_{CK} = t_{CK} \text{ (Min), } BL = Continuo \\ & l_{OUT} = 0 \text{ mA} \end{aligned}$   |                                                                                                                                           | _    | 30   | mA   |

Notes: • All voltages are referenced to Vss = 0 V.

• DC characteristics are measured after following Power-up Timing.

• lout depends on the output load conditions.

#### 2. AC Characteristics

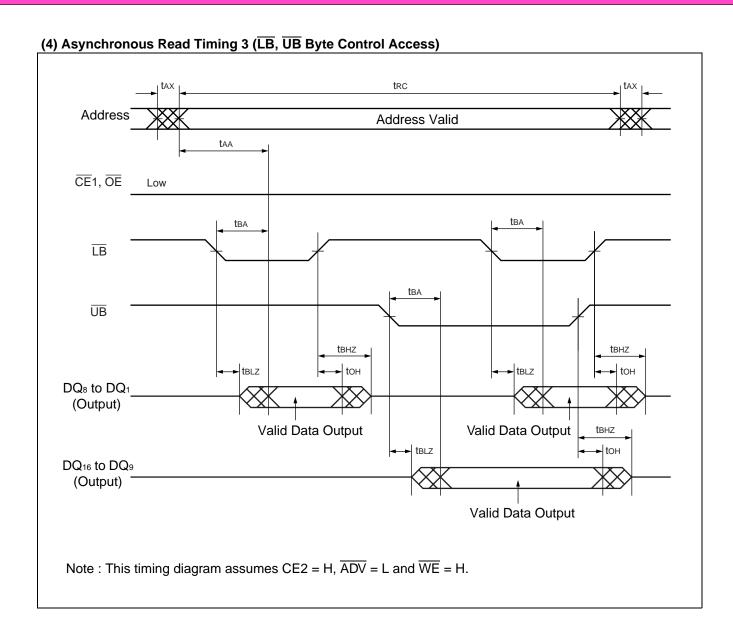

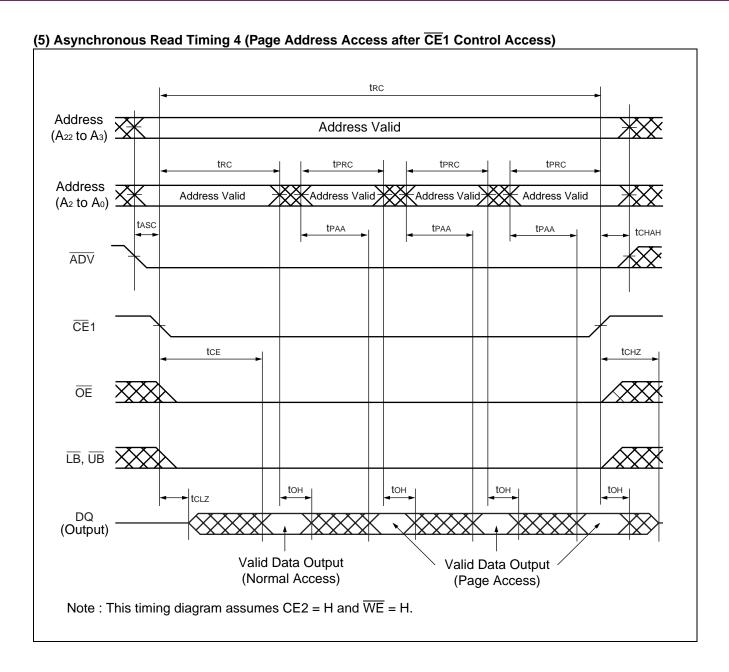

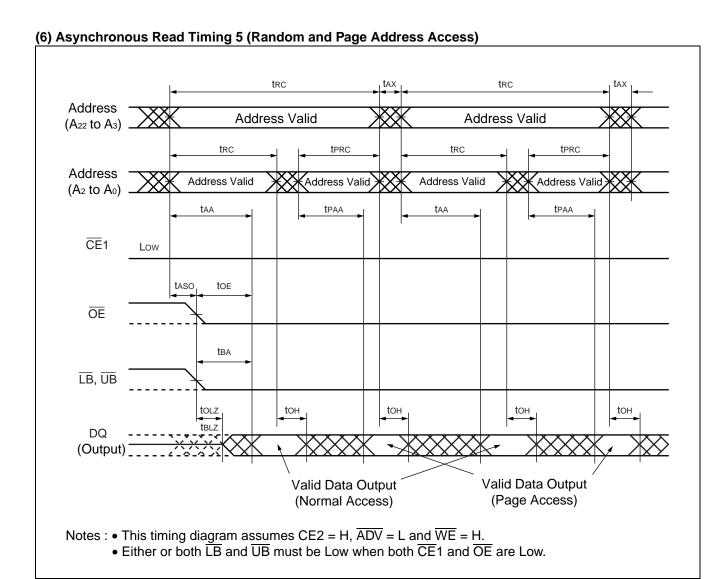

#### (1) Asynchronous Read Operation (Page mode)

(At recommended operating conditions unless otherwise noted)

| ,                               |               | <u> </u>   | lue  | Unit | Notes      |

|---------------------------------|---------------|------------|------|------|------------|

| Parameter                       | Symbol        | Min        | Max  | Unit | Notes      |

| Read Cycle Time                 | <b>t</b> RC   | 70         | 1000 | ns   | *1, *2     |

| CE1 Access Time                 | <b>t</b> ce   | _          | 70   | ns   | *3         |

| OE Access Time                  | <b>t</b> oe   | _          | 40   | ns   | *3         |

| Address Access Time             | <b>t</b> AA   | _          | 70   | ns   | *3, *5     |

| ADV Access Time                 | tav           | _          | 70   | ns   | *3         |

| LB, UB Access Time              | <b>t</b> BA   | _          | 30   | ns   | *3         |

| Page Address Access Time        | <b>t</b> PAA  | _          | 20   | ns   | *3, *6     |

| Page Read Cycle Time            | <b>t</b> PRC  | 20         | 1000 | ns   | *1, *6, *7 |

| Output Data Hold Time           | tон           | 5          | _    | ns   | *3         |

| CE1 Low to Output Low-Z         | <b>t</b> cLZ  | 5          | _    | ns   | *4         |

| OE Low to Output Low-Z          | tolz          | 5          | _    | ns   | *4         |

| LB, UB Low to Output Low-Z      | <b>t</b> BLZ  | 0          | _    | ns   | *4         |

| CE1 High to Output High-Z       | <b>t</b> cHZ  | _          | 20   | ns   | *3         |

| OE High to Output High-Z        | tонz          | _          | 20   | ns   | *3         |

| LB, UB High to Output High-Z    | <b>t</b> BHZ  | _          | 20   | ns   | *3         |

| Address Setup Time to CE1 Low   | tasc          | <b>-</b> 5 | _    | ns   |            |

| Address Setup Time to OE Low    | <b>t</b> aso  | 10         |      | ns   |            |

| ADV Low Pulse Width             | <b>t</b> vpl  | 10         | _    | ns   | *8         |

| ADV High Pulse Width            | tvpн          | 15         | _    | ns   | *8         |

| Address Setup Time to ADV High  | <b>t</b> asv  | 5          | _    | ns   |            |

| Address Hold Time from ADV High | <b>t</b> ahv  | 5          | _    | ns   |            |

| Address Invalid Time            | <b>t</b> AX   | _          | 10   | ns   | *5, *9     |

| Address Hold Time from CE1 High | <b>t</b> CHAH | <b>-</b> 5 | _    | ns   | *10        |

| Address Hold Time from OE High  | <b>t</b> онан | <b>-</b> 5 |      | ns   |            |

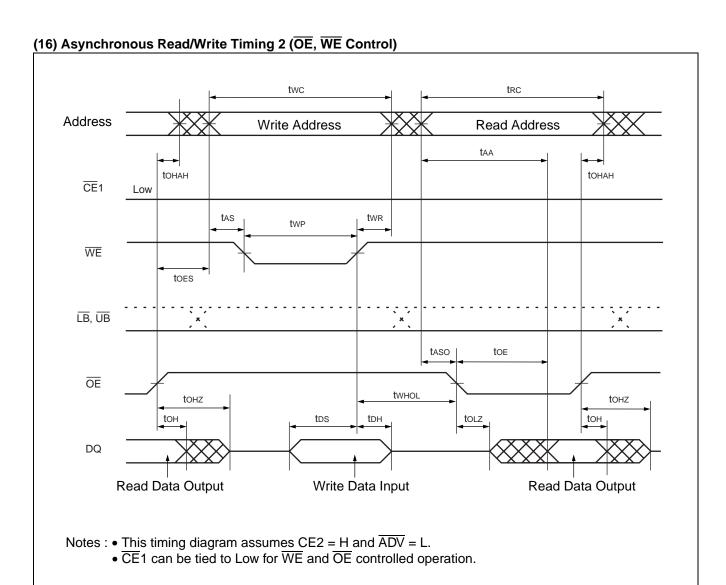

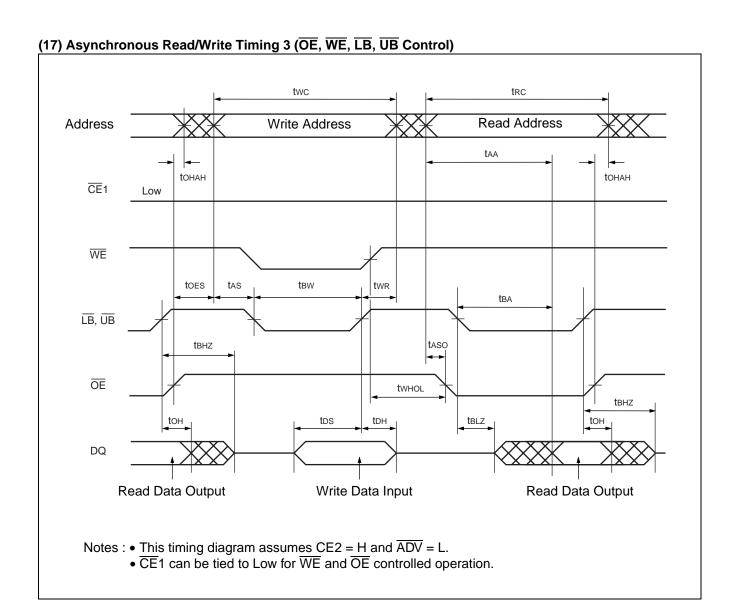

| WE High to OE Low Time for Read | <b>t</b> whol | 25         | 1000 | ns   | *11        |

| CE1 High Pulse Width            | <b>t</b> CP   | 15         |      | ns   |            |

<sup>\*1 :</sup> Maximum value is applicable if  $\overline{\text{CE}}1$  is kept at Low without change of address input of A22 to A3.

(Continued)

<sup>\*2 :</sup> Address should not be changed within minimum tRC.

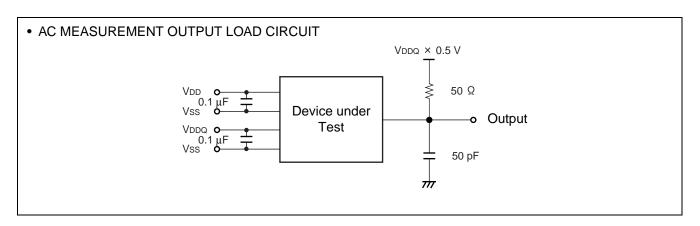

<sup>\*3 :</sup> The output load 50 pF with 50  $\Omega$  termination to VDDQ  $\times$  0.5 V.

<sup>\*4 :</sup> The output load 5 pF without any other load.

<sup>\*5 :</sup> Applicable to  $A_{22}$  to  $A_3$  when  $\overline{CE}1$  is kept at Low.

<sup>\*6 :</sup> Applicable only to  $A_2$ ,  $A_1$  and  $A_0$  when  $\overline{CE}1$  is kept at Low for the page address access.

### (Continued)

- \*7 : In case Page Read Cycle is continued with keeping  $\overline{\text{CE}}1$  stays Low,  $\overline{\text{CE}}1$  must be brought to High within 4  $\mu$ s. In other words, Page Read Cycle must be closed within 4  $\mu$ s.

- \*8 : tvpl is specified from the falling edge of either  $\overline{\text{CE}}1$  or  $\overline{\text{ADV}}$  whichever comes late. The sum of tvpl and tvph must be equal or greater than trc for each access.

- \*9 : Applicable to address access when at least two of address inputs are switched from previous state.

- \*10: trc (Min) and tprc (Min) must be satisfied.

- \*11: If actual value of twhol is shorter than specified minimum values, the actual table of following Read may become longer by the amount of subtracting actual value from specified minimum value.

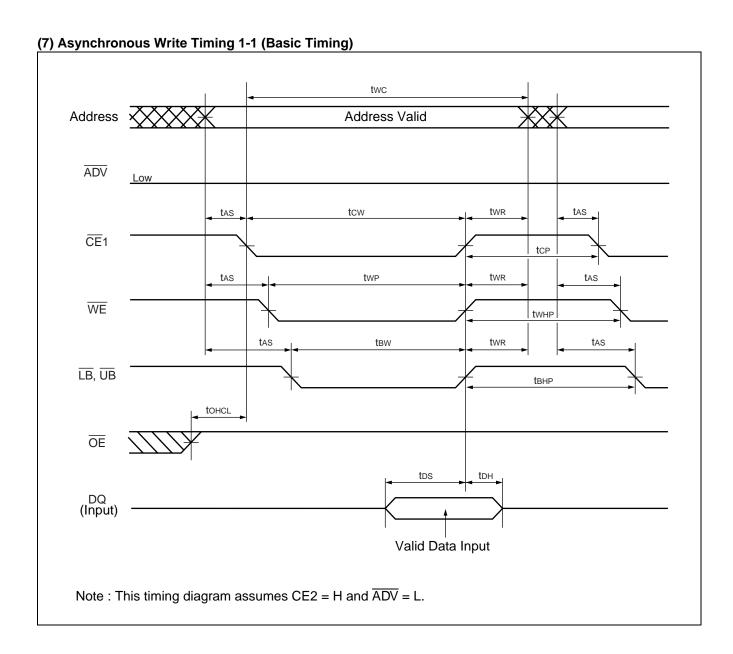

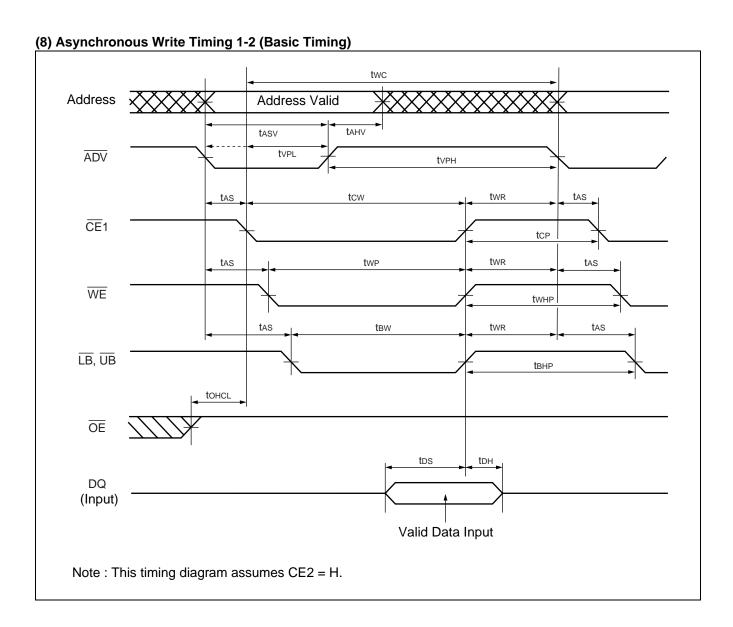

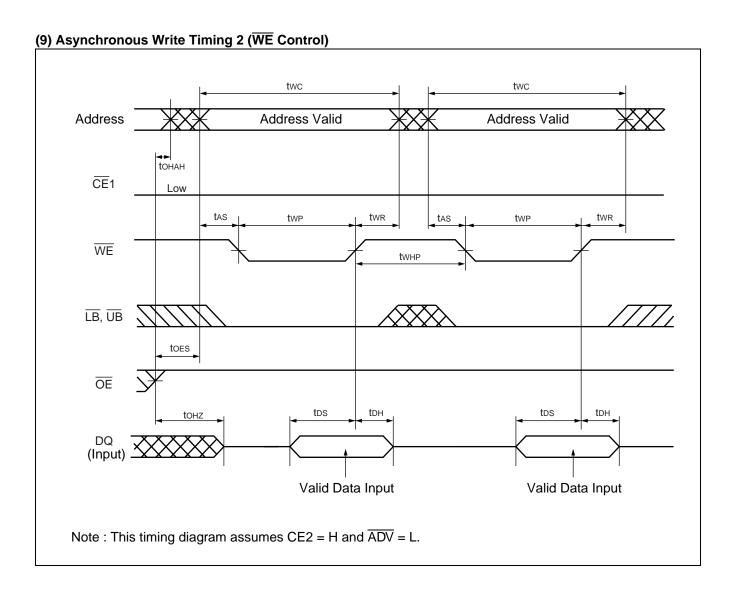

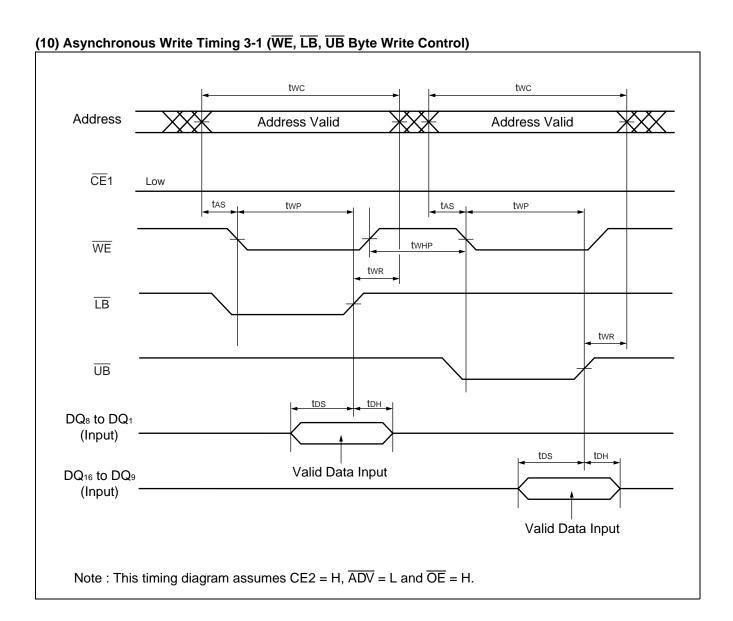

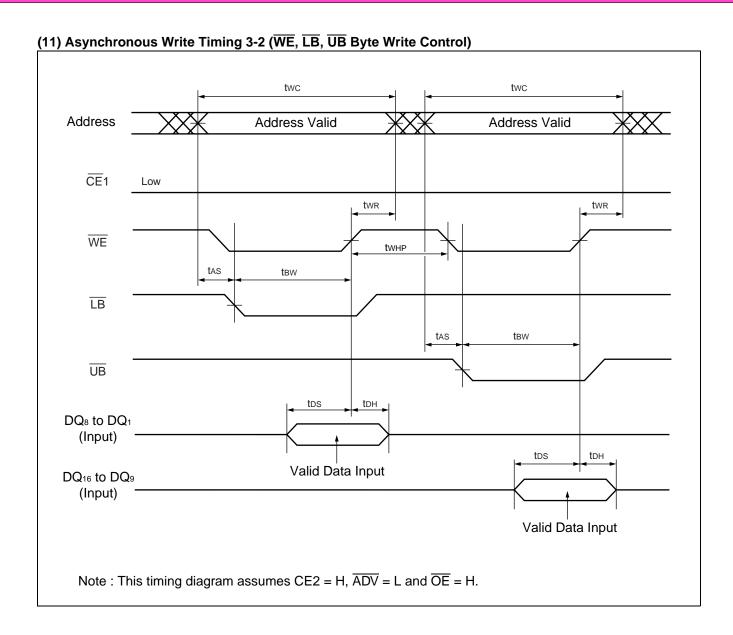

### (2) Asynchronous Write Operation

| Parameter                               | ,                      | Va  | lue  | Unit | Notes  |

|-----------------------------------------|------------------------|-----|------|------|--------|

| Farameter                               | Symbol                 | Min | Max  | Onit | Notes  |

| Write Cycle Time                        | <b>t</b> wc            | 70  | 1000 | ns   | *1, *2 |

| Address Setup Time                      | <b>t</b> AS            | 0   | _    | ns   | *3     |

| ADV Low Pulse Width                     | <b>t</b> vpl           | 10  | _    | ns   | *4     |

| ADV High Pulse Width                    | <b>t</b> vph           | 15  | _    | ns   | *4     |

| Address Setup Time to ADV High          | tasv                   | 5   | _    | ns   |        |

| Address Hold Time from ADV High         | <b>t</b> ahv           | 5   | _    | ns   |        |

| CE1 Write Pulse Width                   | <b>t</b> cw            | 45  | _    | ns   | *3     |

| WE Write Pulse Width                    | <b>t</b> wp            | 45  | _    | ns   | *3     |

| LB, UB Write Pulse Width                | <b>t</b> <sub>BW</sub> | 45  | _    | ns   | *3     |

| Write Recovery Time                     | <b>t</b> wr            | 0   | _    | ns   | *5     |

| CE1 High Pulse Width                    | <b>t</b> cp            | 15  | _    | ns   |        |

| WE High Pulse Width                     | <b>t</b> whp           | 15  | 1000 | ns   |        |

| LB, UB High Pulse Width                 | <b>t</b> внР           | 15  | 1000 | ns   |        |

| Data Setup Time                         | <b>t</b> DS            | 15  | _    | ns   |        |

| Data Hold Time                          | tон                    | 0   | _    | ns   |        |

| OE High to CE1 Low Setup Time for Write | <b>t</b> oncl          | -5  | _    | ns   | *6     |

| OE High to Address Setup Time for Write | toes                   | 0   | _    | ns   | *7     |

| LB and UB Write Pulse Overlap           | <b>t</b> BWO           | 30  | _    | ns   |        |

<sup>\*1:</sup> Maximum value is applicable if  $\overline{CE}1$  is kept at Low without any address change.

<sup>\*2:</sup> Minimum value must be equal or greater than the sum of write pulse width (tcw, twp or tbw) and write recovery time (twr).

<sup>\*3:</sup> Write pulse width is defined from High to Low transition of  $\overline{CE}1$ ,  $\overline{WE}$ ,  $\overline{LB}$ , or  $\overline{UB}$ , whichever occurs last.

<sup>\*4:</sup> tvpL is specified from the falling edge of either  $\overline{\text{CE}}1$  or  $\overline{\text{ADV}}$  whichever comes late. The sum of tvpL and tvpH must be equal or greater than twc for each access.

<sup>\*5:</sup> Write recovery time is defined from Low to High transition of  $\overline{CE}1$ ,  $\overline{WE}$ ,  $\overline{LB}$ , or  $\overline{UB}$ , whichever occurs first.

<sup>\*6:</sup> If  $\overline{OE}$  is Low after minimum tohcl, read cycle is initiated. In other word,  $\overline{OE}$  must be brought to High within 5 ns after  $\overline{CE}1$  is brought to Low.

<sup>\*7:</sup> If  $\overline{OE}$  is Low after new address input, read cycle is initiated. In other word,  $\overline{OE}$  must be brought to High at the same time or before new address is valid.

### (3) Synchronous Operation - Clock Input (Burst mode)

(At recommended operating conditions unless otherwise noted)

| Parameter              |        | Symbol       | Val | lue | Unit  | Notes |

|------------------------|--------|--------------|-----|-----|-------|-------|

| raiailletei            |        | Зуппоот      | Min | Max | Oilit | Notes |

|                        | RL = 5 |              | 13  | _   | ns    | *1    |

| Clock Period           | RL = 4 | <b>t</b> cĸ  | 18  | _   | ns    | *1    |

| Siddict diled          | RL = 3 |              | 30  | _   | ns    | *1    |

| Clock High Pulse Width |        | <b>t</b> скн | 4   | _   | ns    |       |

| Clock Low Pulse Width  |        | <b>t</b> ckL | 4   | _   | ns    |       |

| Clock Transition Time  |        | <b>t</b> скт |     | 3   | ns    | *2    |

<sup>\*1 :</sup> Clock period is defined between valid clock edges.

#### (4) Synchronous Operation - Address Latch (Burst mode)

| Parameter                             | Symbol        | Value |     | Unit | Notes |

|---------------------------------------|---------------|-------|-----|------|-------|

| Farameter                             | Syllibol      | Min   | Max | Onit | Notes |

| Address Setup Time to CE1 Low         | <b>t</b> ascl | -5    | _   | ns   | *1    |

| Address Setup Time to ADV Low         | <b>t</b> asvl | -5    | _   | ns   | *2    |

| Address Hold Time from ADV High       | <b>t</b> ahv  | 5     | _   | ns   |       |

| ADV Low Pulse Width                   | <b>t</b> vpl  | 10    | _   | ns   | *3    |

| ADV Low Setup Time to CLK             | <b>t</b> vsck | 4     | _   | ns   | *4    |

| CE1 Low Setup Time to CLK             | <b>t</b> clck | 4     | _   | ns   | *4    |

| ADV Low Hold Time from CLK            | <b>t</b> ckvh | 1     | _   | ns   | *4    |

| Burst End ADV High Hold Time from CLK | <b>t</b> vhvl | 13    | _   | ns   |       |

<sup>\*1 :</sup>  $t_{ASCL}$  is applicable if  $\overline{CE}1$  is brought to Low after  $\overline{ADV}$  is brought to Low.

<sup>\*2 :</sup> Clock transition time is defined between V<sub>IH</sub> (Min) and V<sub>IL</sub> (Max)

<sup>\*2 :</sup>  $t_{ASVL}$  is applicable if  $\overline{ADV}$  is brought to Low after  $\overline{CE}1$  is brought to Low.

<sup>\*3 :</sup>  $t_{VPL}$  is specified from the falling edge of either  $\overline{CE1}$  or  $\overline{ADV}$  whichever comes late.

<sup>\*4:</sup> Applicable to the 1st valid clock edge.

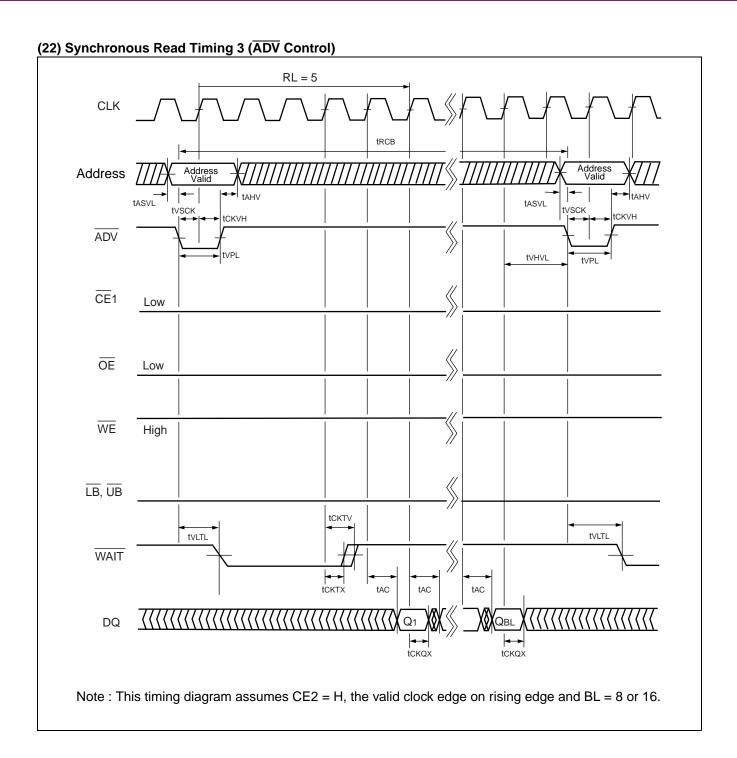

### (5) Synchronous Read Operation (Burst mode)

| Paramete                        | ,               | Symbol           | ed operating<br><b>Va</b> | lue  |                                          | Notes  |

|---------------------------------|-----------------|------------------|---------------------------|------|------------------------------------------|--------|

| Paramete                        | er              | Symbol           | Min                       | Max  | ns n | Notes  |

| Burst Read Cycle Time           |                 | <b>t</b> RCB     | _                         | 8000 | ns                                       |        |

| CLK Access Time                 |                 | <b>t</b> AC      |                           | 11   | ns                                       | *1     |

| Output Hold Time from CLK       |                 | <b>t</b> ckqx    | 3                         | _    | ns                                       | *1     |

| CE1 Low to WAIT Low             |                 | <b>t</b> CLTL    | 5                         | 20   | ns                                       | *1     |

| OE Low to WAIT Low              |                 | <b>t</b> oltl    | 0                         | 20   | ns                                       | *1, *2 |

| ADV Low to WAIT Low             |                 | t∨LTL            | 0                         | 20   | ns                                       | *1     |

| CLK to WAIT Valid Time          |                 | <b>t</b> cktv    | _                         | 11   | ns                                       | *1, *3 |

| WAIT Valid Hold Time from CL    | K               | tсктх            | 3                         | _    | ns                                       | *1     |

| CE1 Low to Output Low-Z         |                 | tclz             | 5                         | _    | ns                                       | *4     |

| OE Low to Output Low-Z          |                 | tolz             | 5                         | _    | ns                                       | *4     |

| LB, UB Low to Output Low-Z      |                 | <b>t</b> BLZ     | 0                         | _    | ns                                       | *4     |

| CE1 High to Output High-Z       |                 | <b>t</b> cHZ     | _                         | 20   | ns                                       | *1     |

| OE High to Output High-Z        |                 | <b>t</b> onz     | _                         | 20   | ns                                       | *1     |

| LB, UB High to Output High-Z    |                 | <b>t</b> BHZ     | _                         | 20   | ns                                       | *1     |

| CE1 High to WAIT High-Z         |                 | <b>t</b> chtz    | _                         | 20   | ns                                       | *1     |

| OE High to WAIT High-Z          |                 | tонтz            | _                         | 20   | ns                                       | *1     |

| OE Low Setup Time to 1st Data   | a-output        | <b>t</b> olq     | 30                        | _    | ns                                       |        |

| LB, UB Setup Time to 1st Data   | -output         | <b>t</b> BLQ     | 26                        | _    | ns                                       | *5     |

| OE Setup Time to CLK            |                 | <b>t</b> osck    | 4                         | _    | ns                                       |        |

| OE Hold Time from CLK           |                 | tскон            | 2                         |      | ns                                       |        |

| Burst End CE1 Low Hold Time     | from CLK        | <b>t</b> ckclh   | 2                         | _    | ns                                       |        |

| Burst End LB, UB Hold Time from | om CLK          | <b>t</b> сквн    | 2                         | _    | ns                                       |        |

| Burst Terminate                 | BL = 8, 16      | t <sub>TRB</sub> | 26                        | _    | ns                                       | *6     |

| Recovery Time                   | BL = Continuous | LIKB             | 70                        |      | ns                                       | *6     |

<sup>\*1 :</sup> The output load 50 pF with 50  $\Omega$  termination to  $V_{\text{DDQ}} \times 0.5 \text{ V.}$

<sup>\*2 :</sup> WAIT drives High at the beginning depending on OE falling edge timing.

<sup>\*3:</sup> tcktv is guaranteed after toltl (Max) from  $\overline{\text{OE}}$  falling edge and tosck must be satisfied.

<sup>\*4 :</sup> The output load 5 pF without any other load.

<sup>\*5 :</sup> Once they are determined, they must not be changed until the end of burst read.

<sup>\*6 :</sup> Defined from the Low to High transition of  $\overline{\text{CE}}1$  to the High to Low transition of either  $\overline{\text{ADV}}$  or  $\overline{\text{CE}}1$  whichever occurs late.

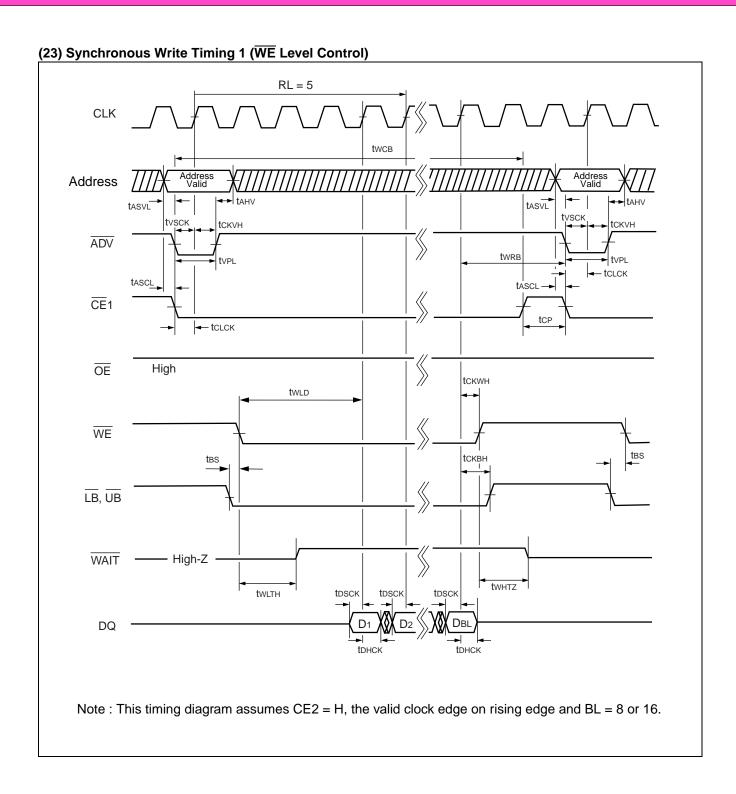

### (6) Synchronous Write Operation (Burst mode)

| Parameter                           |                  | Commende       | Value |      |      |       |

|-------------------------------------|------------------|----------------|-------|------|------|-------|

| Para                                | meter            | Symbol         | Min   | Max  | Unit | Notes |

| Burst Write Cycle Time              |                  | twcв           | _     | 8000 | ns   |       |

| Data Setup Time to CLK              |                  | <b>t</b> DSCK  | 5     | _    | ns   |       |

| Data Hold Time from CLK             |                  | <b>t</b> DHCK  | 3     | _    | ns   |       |

| WE Low Setup Time to 1s             | t Data Input     | twld           | 30    | _    | ns   |       |

| LB, UB Setup Time for Wr            | ite              | <b>t</b> BS    | -5    | _    | ns   | *1    |

| WE Setup Time to CLK                |                  | twsck          | 4     | _    | ns   |       |

| WE Hold Time from CLK               |                  | <b>t</b> ckwh  | 2     | _    | ns   |       |

| CE1 Low to WAIT High                |                  | <b>t</b> clth  | 5     | 20   | ns   | *2    |

| WE Low to WAIT High                 |                  | <b>t</b> wlth  | 0     | 20   | ns   | *2    |

| CE1 High to WAIT High-Z             |                  | <b>t</b> chtz  | _     | 20   | ns   | *2    |

| WE High to WAIT High-Z              |                  | <b>t</b> whtz  | _     | 20   | ns   | *2    |

| Burst End CE1 Low Hold              | Γime from CLK    | <b>t</b> ckclh | 2     | _    | ns   |       |

| Burst End CE1 High Setup            | Time to next CLK | tchck          | 4     | _    | ns   |       |

| Burst End LB, UB Hold Time from CLK |                  | tсквн          | 2     |      | ns   |       |

| Burst Write Recovery Time           |                  | twrb           | 26    | _    | ns   | *3    |

| Burst Terminate                     | BL = 8, 16       | <b>t</b> TRB   | 26    | _    | ns   | *4    |

| Recovery Time                       | BL = Continuous  | <b>t</b> TRB   | 70    | _    | ns   | *4    |

<sup>\*1 :</sup> Defined from the valid input edge to the High to Low transition of either  $\overline{ADV}$ ,  $\overline{CE}1$ , or  $\overline{WE}$ , whichever occurs last. And once  $\overline{LB}$ ,  $\overline{UB}$  are determined,  $\overline{LB}$ ,  $\overline{UB}$  must not be changed until the end of burst write.

<sup>\*2 :</sup> The output load 50 pF with 50  $\Omega$  termination to  $V_{DDQ} \times 0.5 \text{ V}$ .

<sup>\*3 :</sup> Defined from the valid clock edge where last data-input being latched at the end of burst write to the High to Low transition of either ADV or CE1 whichever occurs late for the next access.

<sup>\*4 :</sup> Defined from the Low to High transition of  $\overline{\text{CE}}1$  to the High to Low transition of either  $\overline{\text{ADV}}$  or  $\overline{\text{CE}}1$  whichever occurs late for the next access.

#### (7) Power Down Parameters

(At recommended operating conditions unless otherwise noted)

| Parameter                                                                       | Symbol        | Value |     | Unit  | Notes |

|---------------------------------------------------------------------------------|---------------|-------|-----|-------|-------|

| Farameter                                                                       | Syllibol      | Min   | Max | Oille | Notes |

| CE2 Low Setup Time for Power Down Entry                                         | <b>t</b> csp  | 20    | _   | ns    | *1    |

| CE2 Low Hold Time after Power Down Entry                                        | <b>t</b> C2LP | 70    |     | ns    | *1    |

| CE1 High Hold Time following CE2 High after Power Down Exit [SLEEP mode only]   | tснн          | 300   | _   | μs    | *1    |

| CE1 High Hold Time following CE2 High after Power Down Exit [not in SLEEP mode] | tсннр         | 70    | _   | ns    | *2    |

| CE1 High Setup Time following CE2 High after Power Down Exit                    | <b>t</b> chs  | 0     | _   | ns    | *1    |

<sup>\*1:</sup> Applicable also to power-up.

#### (8) Other Timing Parameters

| Parameter                                            | Symbol            | Value |     | Unit  | Notes  |

|------------------------------------------------------|-------------------|-------|-----|-------|--------|

| raiametei                                            | Syllibol          | Min   | Max | Oilit | Notes  |

| CE1 High to OE Invalid Time for Standby Entry        | <b>t</b> cHOX     | 10    | _   | ns    |        |

| CE1 High to WE Invalid Time for Standby Entry        | <b>t</b> chwx     | 10    | _   | ns    | *1     |

| CE2 High Hold Time after Power-up                    | t <sub>C2HL</sub> | 50    | _   | μs    |        |

| CE1 High Hold Time following CE2 High after Power-up | tснн              | 300   | _   | μs    |        |

| Input Transition Time (except for CLK)               | t⊤                | 1     | 25  | ns    | *2, *3 |

<sup>\*1 :</sup> Some data might be written into any address location if tchwx (Min) is not satisfied.

<sup>\*2:</sup> Applicable when 16 M-bit or 32 M-bit Partial mode is set.

<sup>\*2 :</sup> Except for CLK input transition time.

<sup>\*3 :</sup> The Input Transition Time (t<sub>T</sub>) at AC testing is 5 ns for Asynchronous operation and 3 ns for Synchronous operation respectively. If actual t<sub>T</sub> is longer than 5 ns or 3 ns specified as AC test condition, it may violate AC specification of some timing parameters. See " (9) AC Test Conditions".

### (9) AC Test Conditions

| Description                |                     | Symbol | Test Setup          | Value                                         | Unit   | Notes |  |

|----------------------------|---------------------|--------|---------------------|-----------------------------------------------|--------|-------|--|

| Input High Level           |                     |        | _                   | $V_{\text{DDQ}} \times 0.8$                   | V      |       |  |

| Input Low Level            |                     | VIL    | _                   | $V_{\text{DDQ}} \times 0.2$                   | V      |       |  |

| Input Timing Measurement L | g Measurement Level |        | _                   | $V_{\text{DDQ}} \times 0.5$                   | V      |       |  |

| Input Transition Time      | Async.              |        | t- Dotw             | Between V <sub>I</sub> L and V <sub>I</sub> H | 5      | ns    |  |

| Input Transition Time      | Sync.               | tr     | Detween VIL and VIH | 3                                             | V<br>V |       |  |

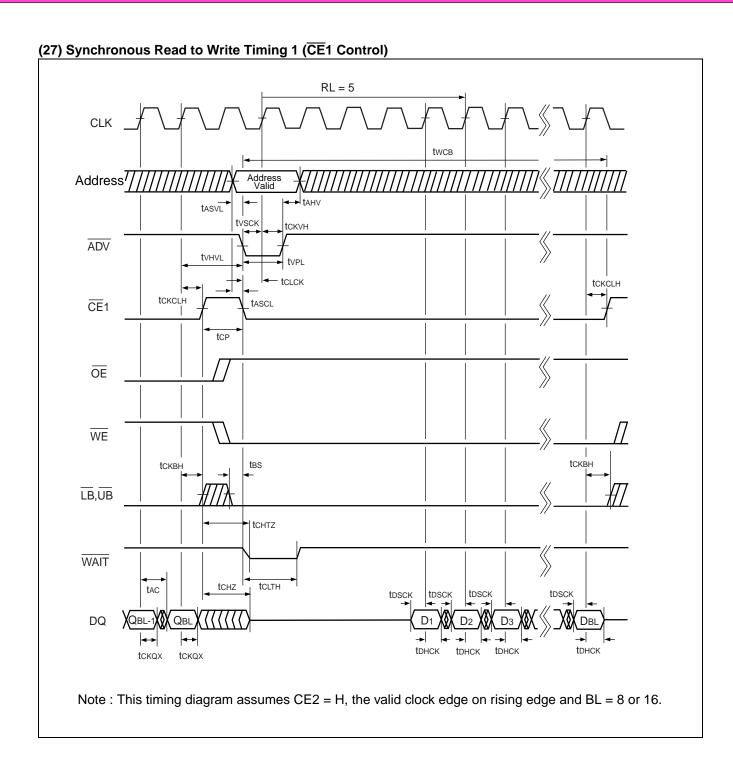

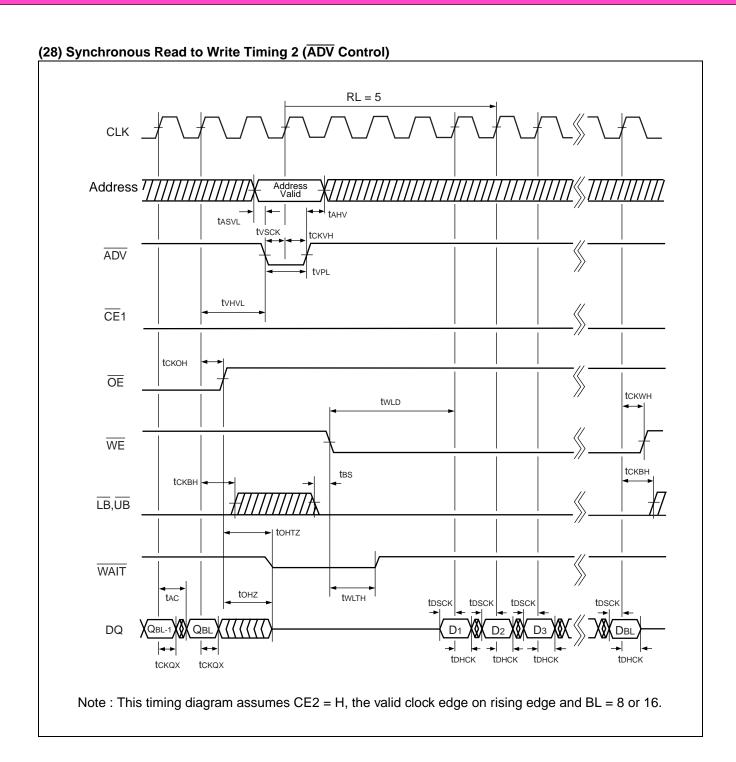

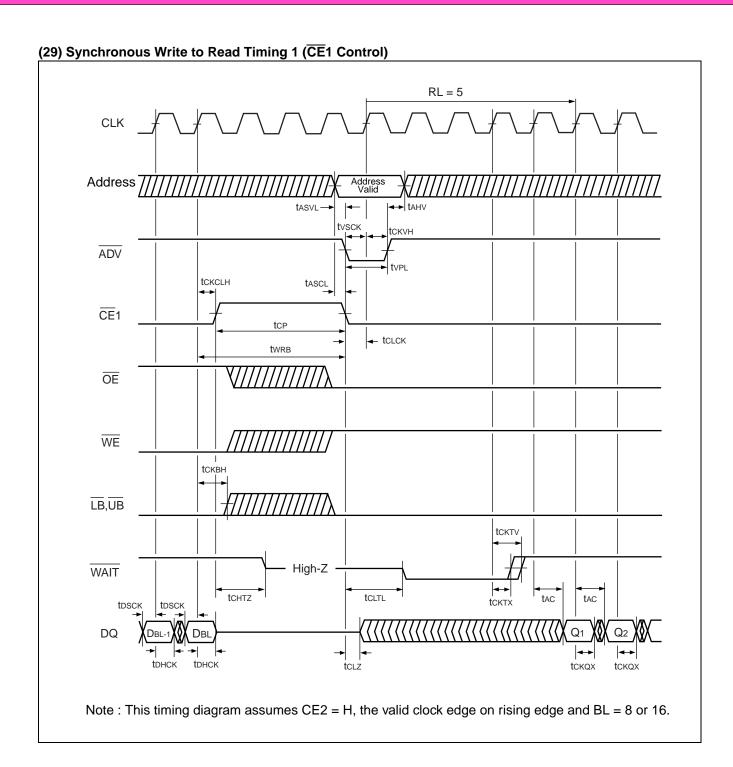

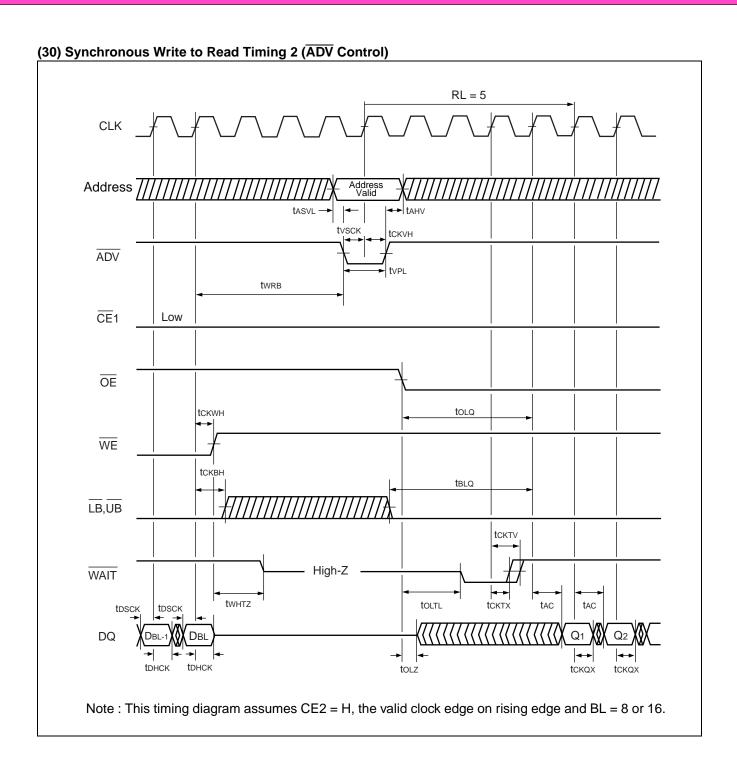

### **■ TIMING DIAGRAMS**

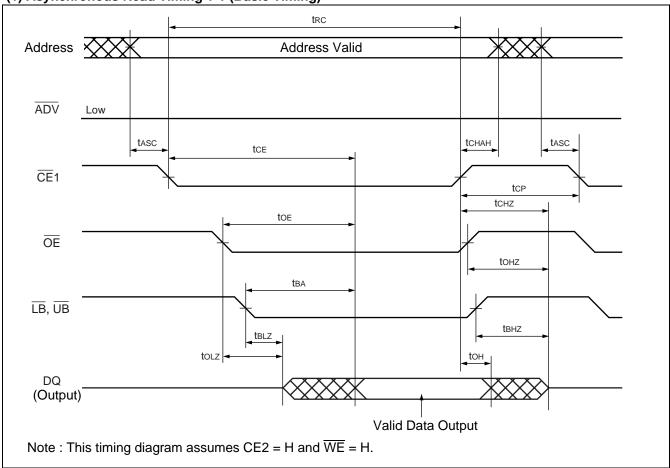

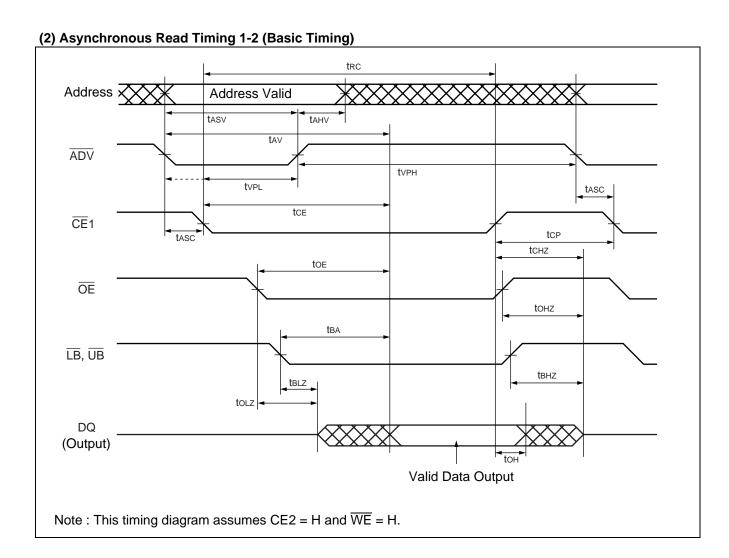

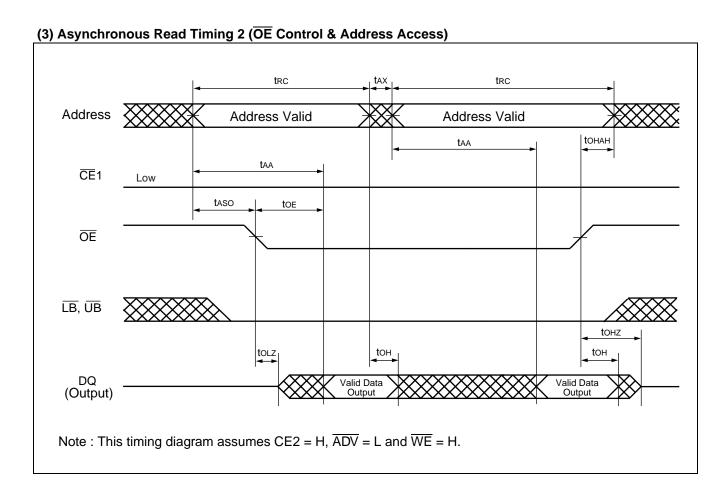

### (1) Asynchronous Read Timing 1-1 (Basic Timing)

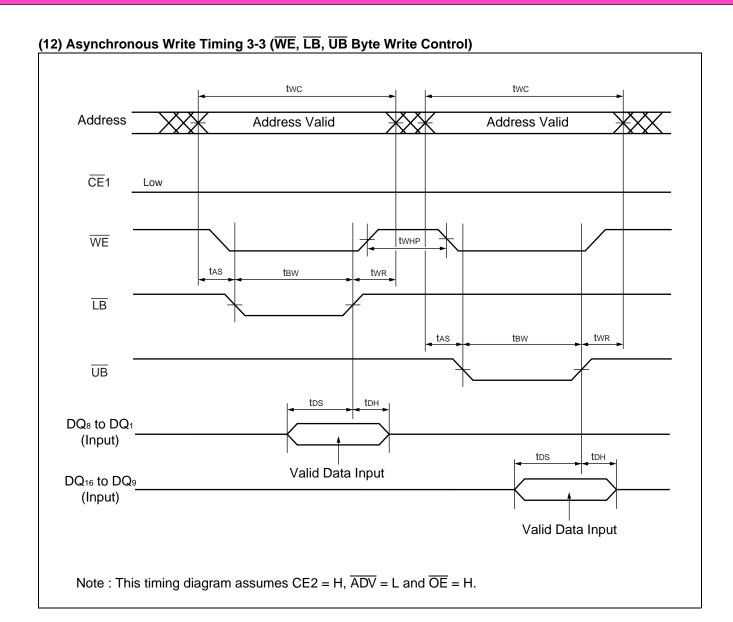

#### (13) Asynchronous Write Timing 3-4 (WE, LB, UB Byte Write Control) twc twc Address Address Valid Address Valid CE<sub>1</sub> Low WE tBW tBW tas twR tas twR LB tBHP tbwo tos tos tDH\_ tDH . DQ<sub>8</sub> to DQ<sub>1</sub> Valid Data Input Valid Data Input (Input) tBWO tBW tBW tas tas twR twR UB tBHP tos $DQ_{16}$ to $DQ_{9}$ Valid Data Input Valid Data Input (Input) Note: This timing diagram assumes CE2 = H, $\overline{ADV} = L$ and $\overline{OE} = H$ .

### (15) Asynchronous Read/Write Timing 1-2 (CE1, WE, OE Control) twc tRC Address Write Address Read Address tCHAH tas **t**CHAH tce CE<sub>1</sub> tcp tcp twp $\overline{\text{WE}}$ LB, UB tohcl toe ŌĒ tchz tolz ton tDS tDH ton DQ Read Data Output Write Data Input Read Data Output Notes: • This timing diagram assumes CE2 = H and $\overline{ADV} = L$ . • OE can be fixed Low during write operation if it is CE1 controlled write at Read-Write-Read sequence.

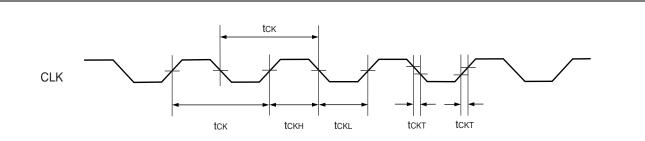

#### (18) Clock Input Timing

Notes : • Stable clock input must be required during  $\overline{CE}1 = L$ .

- tck is defined between valid clock edges.

- tckt is defined between ViH (Min) and ViL (Max).

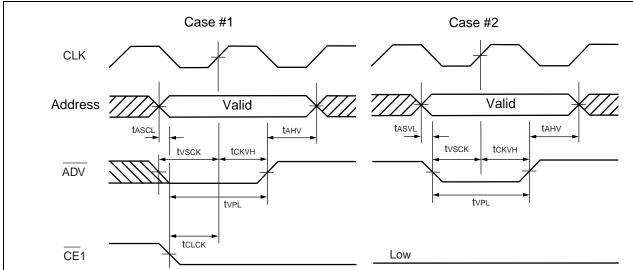

#### (19) Address Latch Timing (Synchronous Mode)

Notes: • Case #1 is the timing when  $\overline{CE1}$  is brought to Low after  $\overline{ADV}$  is brought to Low. Case #2 is the timing when  $\overline{ADV}$  is brought to Low after  $\overline{CE1}$  is brought to Low.

- typl is specified from the falling edge of either  $\overline{CE1}$  or  $\overline{ADV}$  whichever comes late. At least one valid clock edge must be input during  $\overline{ADV} = L$ .

- tvsck and tclck are applied to the 1st valid clock edge during ADV=L.

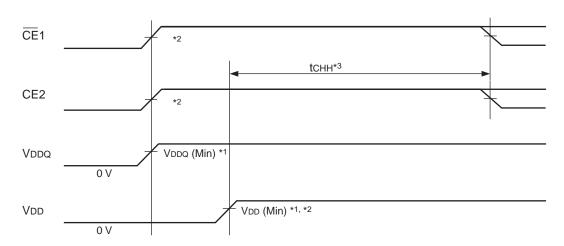

#### (31) Power-up Timing 1

- $^{*}1$ :  $V_{DDQ}$  shall be applied and reached the specified minimum level prior to  $V_{DD}$  applied.

- \*2: The both of  $\overline{\text{CE}}1$  and CE2 shall be brought to High together with  $V_{DDQ}$  prior to  $V_{DD}$  applied. Otherwise "(32) Power-up Timing 2" must be applied for proper operation.

- \*3: The tchh specifies after VDD reaches specified minimum level and applicable to both  $\overline{\text{CE}}1$  and CE2.

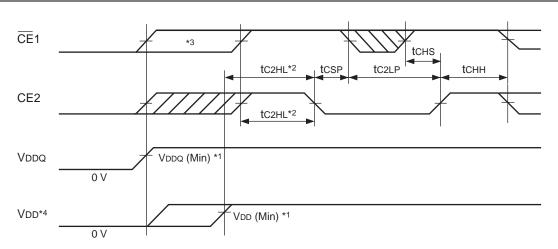

#### (32) Power-up Timing 2

- \*1: VDDQ shall be applied and reached the specified minimum level prior to VDD applied.

- \*2: The tc2HL specifies from CE2 Low to High transition after VDD reaches specified minimum level. If CE2 became High prior to VDD reached specified minimum level, tc2HL is defined from VDD minimum.

- \*3: CE1 shall be brought to High prior to or together with CE2 Low to High transition.

- \*4: If transition time of V<sub>DD</sub> (from 0 V to V<sub>DD</sub> (Min)) is longer than 10 ms, "(31) Power-up Timing 1" must be applied.

#### (33) Power Down Entry and Exit Timing

Note: This Power Down mode can be also used as a reset timing if "Power-up timing" above could not be satisfied and Power Down program was not performed prior to this reset.

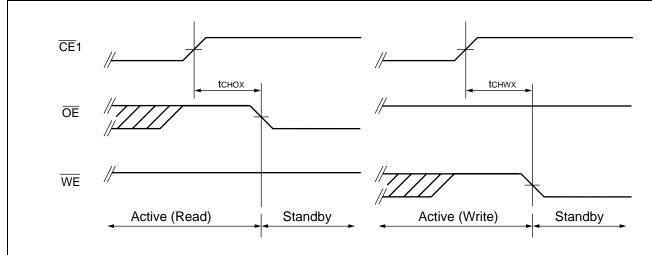

### (34) Standby Entry Timing after Read or Write

Note: Both tchox and tchwx define the earliest entry timing for Standby mode.

- \*1: The all address inputs must be High from Cycle #1 to #5.

- \*2: The address key must confirm the format specified in "**TFUNCTIONAL DESCRIPTION**". If not, the operation and data are not guaranteed.

- \*3: After tcp or tRc following Cycle #6, the Configuration Register Set is completed and returned to the normal operation. tcp and tRc are applicable to returning to asynchronous mode and to synchronous mode respectively.

- \*4: Byte read or write is available in addition to Word read or write. At least one byte control signal (LB or UB) need to be Low.

- \*1: The all address inputs must be High from Cycle #1 to #5.

- \*2: The address key must confirm the format specified in "■FUNCTIONAL DESCRIPTION". If not, the operation and data are not guaranteed.

- \*3: After ttrb following Cycle #6, the Configuration Register Set is completed and returned to the normal operation.

- \*4: Byte read or write is available in addition to Word read or write. At least one byte control signal (LB or UB) need to be Low.

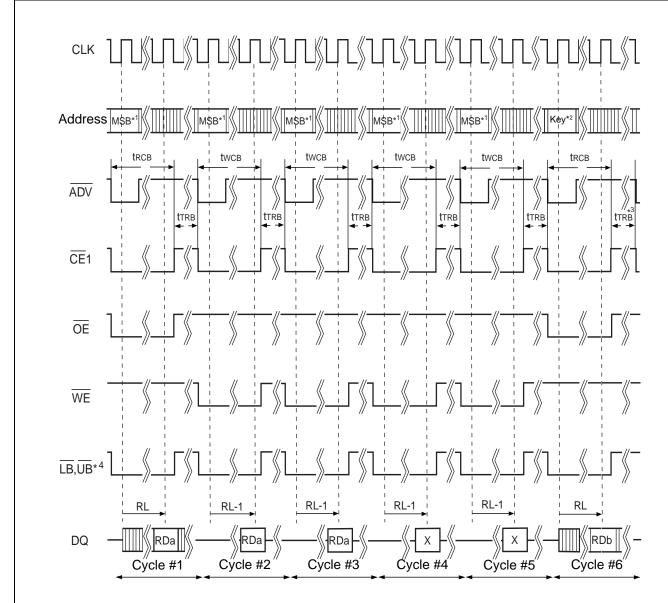

#### **■ PACKAGE FOR ENGINEERING SAMPLES**

• Pin Assignment

### • Pin Description

| Pin Name                            | Description                      |  |  |  |

|-------------------------------------|----------------------------------|--|--|--|

| A <sub>22</sub> to A <sub>0</sub>   | Address Input                    |  |  |  |

| CE1                                 | Chip Enable 1 (Low Active)       |  |  |  |

| CE2                                 | Chip Enable 2 (High Active)      |  |  |  |

| WE                                  | Write Enable (Low Active)        |  |  |  |

| ŌĒ                                  | Output Enable (Low Active)       |  |  |  |

| LB                                  | Lower Byte Control (Low Active)  |  |  |  |

| ÜB                                  | Upper Byte Control (Low Active)  |  |  |  |

| CLK                                 | Clock Input                      |  |  |  |

| ĀDV                                 | Address Valid Input (Low Active) |  |  |  |

| WAIT                                | Wait Output                      |  |  |  |

| DQ <sub>8</sub> to DQ <sub>1</sub>  | Lower Byte Data Input/Output     |  |  |  |

| DQ <sub>16</sub> to DQ <sub>9</sub> | Upper Byte Data Input/Output     |  |  |  |

| V <sub>DD</sub>                     | Power Supply Voltage             |  |  |  |

| VDDQ                                | I/O Power Supply Voltage         |  |  |  |

| Vss                                 | Ground                           |  |  |  |

| N.C.                                | No Connection                    |  |  |  |

### • Package Capacitance

$(f = 1 \text{ MHz}, T_A = +25 ^{\circ}C)$

| Parameter                     | Symbol           | Test conditions       | Value |     |     | Unit  |

|-------------------------------|------------------|-----------------------|-------|-----|-----|-------|

|                               |                  |                       | Min   | Тур | Max | Uiiii |

| Address Input Capacitance     | C <sub>IN1</sub> | V <sub>IN</sub> = 0 V | _     | _   | 5   | pF    |

| Control Input Capacitance     | C <sub>IN2</sub> | VIN = 0 V             | _     | _   | 5   | pF    |

| Data Input/Output Capacitance | Cı/o             | Vio = 0 V             | _     | _   | 8   | pF    |

### • Package View

#### **■ ORDERING INFORMATION**

| Part Number         | Shipping Form | Remarks |

|---------------------|---------------|---------|

| MB82DBR08163A-70LWT | wafer         |         |

## **FUJITSU LIMITED**

All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of Fujitsu semiconductor device; Fujitsu does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. Fujitsu assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of Fujitsu or any third party or does Fujitsu warrant non-infringement of any third-party's intellectual property right or other right by using such information. Fujitsu assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

#### F0601